## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

## EZ-PD<sup>™</sup> BCR Datasheet

USB Type-C Port Controller for Power Sinks

## **General Description**

EZ-PD<sup>™</sup> BCR is Cypress' highly-integrated pre-programmed USB Type-C port controller targeting electronic devices that have legacy barrel connectors (up to 100W) or USB micro-B connectors for power such as drones, smart speakers, power tools, and other rechargeable devices. EZ-PD BCR complies with the latest USB Type-C and USB Power Delivery (PD) standards and enables users to quickly convert their devices from being powered through a barrel connector to being powered via the USB-C connector with few external components and no firmware development is required. EZ-PD BCR integrates a complete USB Type-C transceiver, USB PD policy manager, a load switch controller with a soft start, all termination resistors required for a USB Type-C port, and system-level ESD protection. It is available in a 24-pin QFN package.

#### Features

#### USB Type-C and USB-PD Support

- Supports USB PD3.0 Revision 2.0 Version 1.3

- Configurable resistor R<sub>D</sub>

- Supports one USB Type-C port

#### **5V Legacy Charging**

■ Supports 5-V operation when connected to USB Type-A ports

#### **System-Level Fault Protection**

- VBUS to CC Short Protection

- On-chip overvoltage protection (OVP)

#### **Clocks and Oscillators**

■ Integrated oscillator eliminating the need for external clock

#### Power

■ 3.0-V to 24.5-V operation (30-V tolerant)

#### System-Level ESD Protection

- On CC, VBUS\_IN, DC\_OUT, D+, D-, HPI\_SDA and HPI\_SCL pins

- ± 8-kV contact discharge and ±15-kV air gap discharge based on IEC61000-4-2 level 4C

#### Packages

- 24-pin QFN package

- Supports extended industrial temperature range (-40°C to +105°C)

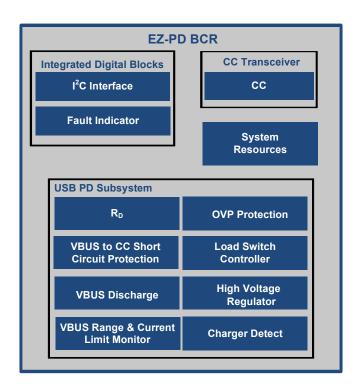

## Logic Block Diagram

## Contents

| Functional Overview                | 3 |

|------------------------------------|---|

| USB-PD Subsystem                   |   |

| Integrated I <sup>2</sup> C Blocks |   |

| Power Systems Overview             |   |

| Pinouts                            |   |

| Application Overview               | 7 |

| Electrical Specifications          |   |

| Absolute Maximum Ratings           |   |

| Device-Level Specifications        |   |

| Digital Peripherals                |   |

| System Resources                   |   |

| Ordering Information               |   |

| Ordering Code Definitions          |   |

| Packaging                               | 19 |

|-----------------------------------------|----|

| Acronyms                                | 21 |

| Document Conventions                    | 21 |

| Units of Measure                        | 21 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 23 |

| Products                                | 23 |

| PSoC® Solutions                         | 23 |

| Cypress Developer Community             | 23 |

| Technical Support                       | 23 |

|                                         |    |

### **Functional Overview**

#### USB-PD Subsystem

The USB-PD subsystem provides the interface to the USB Type-C USB port. This subsystem comprises a high-voltage regulator, OVP, and supply switch blocks. This subsystem also includes all ESD protection required and supported on the USB Type-C port.

#### USB-PD Physical Layer

The USB-PD Physical Layer consists of a transmitter and receiver that communicate BMC-encoded data over the CC channel based on the USB PD 3.0 standard. All communication is half-duplex. The Physical Layer or PHY practices collision avoidance to minimize communication errors on the channel.

The USB-PD block includes the termination resistor  $R_D$  and its switch as required by the USB-PD spec.  $R_D$  resistor is required to implement connection detection, plug orientation detection, and for establishing USB UFP role.

According to the USB Type-C spec, a USB Type-C controller such as the EZ-PD BCR device must present certain termination resistors depending on its role in its unpowered state. The Sink role requires  $R_D$  resistor to be present on the CC pins even in an unpowered state. To implement this function, EZ-PD BCR has a dead battery  $R_D$  resistor bonded to both the CC pins.

#### VBUS Overvoltage Protection

The EZ-PD BCR device has an integrated hardware block for VBUS OVP with configurable thresholds and response times on the USB Type-C port.

#### **VBUS Short Protection**

The EZ-PD BCR device provides VBUS short protection on CC1 an CC2 pins. These pins are protected from accidental shorts to high-voltage VBUS. Accidental shorts may occur because the CC1 and CC2 pins are placed next to the VBUS pins in the USB Type-C connector. A USB-PD controller without the high-voltage VBUS short protection will be damaged in the event of accidental shorts. When the protection circuit is triggered, the EZ-PD BCR device can handle up to 17 V forever and between 17 V to 22 VDC for 1000 hours on the CC1 and CC2 pins. When a VBUS short event occurs on the CC pins, a temporary high-ringing voltage is observed due to the RLC elements in the USB Type-C cable. Without the EZ-PD BCR device connected, this ringing voltage can be twice (44 V) the maximum VBUS voltage (21.5 V). However, when the EZ-PD BCR device is connected, it is capable of clamping temporary high-ringing voltage and protecting the CC pin using IEC ESD protection diodes.

#### Sink Load Switch Controller on VBUS Path

The EZ-PD BCR device has an integrated load switch controller to drive external PFETs on the VBUS sink path. This load switch controller has a soft start feature that limits the in-rush current flowing through the sink power path when the system is connected to an external load and powered on.

#### SAFE\_PWR\_EN Gate Driver

The EZ-PD BCR device has a SAFE\_PWR\_EN gate driver that can be used to drive an alternate load switch/FET. It is enabled whenever the EZ-PD BCR device is unable to negotiate the requested power contract. In such a scenario, the EZ-PD BCR device negotiates a 5-V/900-mA contract which can be delivered through the SAFE\_PWR\_EN FET to an alternate power rail in the system. This allows the system to operate in a limited mode when the requested power is unavailable through the USB Type-C port.

#### VBUS Discharge FETs

The EZ-PD BCR device also has an integrated VBUS discharge FET used to discharge VBUS to meet the USB-PD specification timing on a detach condition.

#### Integrated I<sup>2</sup>C Blocks

The EZ-PD BCR device has an  $I^2$ C slave interface that can be connected to an  $I^2$ C host. The slave address is 0x08. Contact Cypress Technical Support for further details related with EZ-PD BCR HPI specification.

The I<sup>2</sup>C interface is capable of operating at speeds of up to 1 Mbps (Fast-mode Plus). The I<sup>2</sup>C interface is also compatible with the I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I<sup>2</sup>C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/Os are implemented with GPIO in open-drain modes.

The  $I^2C$  interface is not completely compliant with the  $I^2C$  spec in the following aspects:

- Fast-mode Plus has an I<sub>OL</sub> specification of 20 mA at a V<sub>OL</sub> of 0.4 V. The GPIO cells can sink a maximum of 8-mA I<sub>OL</sub> with a V<sub>OL</sub> maximum of 0.6 V.

- Fast-mode and Fast-mode Plus specify minimum Fall times, which are not met with the GPIO cell; Slow strong mode can help meet this spec depending on the bus load.

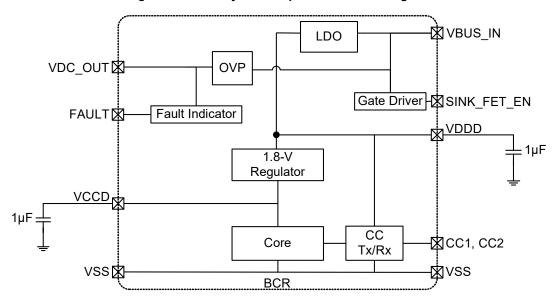

## **Power Systems Overview**

The EZ-PD BCR device can operate from two possible external supply sources: VBUS\_IN (3.0 V–24.5 V) or VDDD (2.7 V–5.5 V). When powered through VBUS\_IN, the internal regulator generates VDDD of 3.3 V for chip operation. The regulated supply, VDDD, is either used directly inside some analog blocks or further regulated down to VCCD (1.8 V), which powers majority of the core using the regulators. Refer to the application diagram (see Figure 3) for capacitor connections.

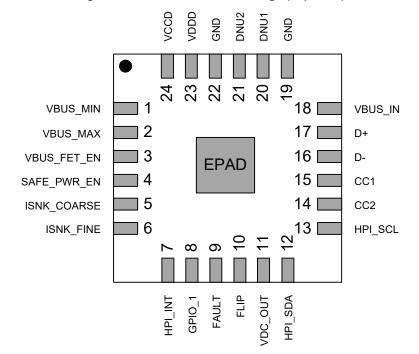

## Pinouts

#### Table 1. EZ-PD BCR Pin Descriptions

| 24-Pin QFN | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VBUS_MIN    | Connect a resistor divider on this to 3.3 V (from the VDDD pin) to indicate the minimum voltage needed by the system from the attached power adapter.<br>Refer to Table 2 for recommended resistor values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2          | VBUS_MAX    | Connect a resistor divider on this to 3.3 V (from the VDDD pin) to indicate the maximum voltage needed by the system from the attached power adapter.<br>Refer to Table 2 for recommended resistor values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3          | VBUS_FET_EN | Connect this signal to the gate of a FET through a series resistor. This pin is the output of a PMOS FET gate driver that is slew-rate controlled.<br>This signal is enabled when the EZ-PD BCR device successfully negotiates a power contract within the requested range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4          | SAFE_PWR_EN | Connect this signal to the gate of a FET through a series resistor. This pin is the output of a PMOS FET gate driver.<br>This signal is enabled when the EZ-PD BCR device fails to negotiate for higher power and defaults to 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5          | ISNK_COARSE | Connect a resistor divider on these pins to 3.3 V (from the VDDD pin) to set the operating current requested from the power adapter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6          | ISNK_FINE   | Refer toTable 3 and Table 4 for recommended resistor values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7          | HPI_INT     | Active LOW HPI Interrupt pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8          | GPIO_1      | Additional GPIO that can be set up over the HPI interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9          | FAULT       | The EZ-PD BCR device pulls this line high if the power adapter cannot supply the required voltage or current or if an OVP event was detected. The pin is low otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10         | FLIP        | The EZ-PD BCR device pulls this line low if no device is attached or if CC polarity is un-flipped (CC1 connected). If a device is attached on CC2 (polarity is flipped), the EZ-PD BCR device pulls this line high.<br>This is an open drain I/O that requires an external pull-up resistor. The presence or the value of the pull-up resistor connected to this pin determines the data capability reported in the UFP Vendor Data Object (VDO) by the BCR device to the Downstream Facing Port (DFP).<br>If there is no pull-up resistor on this pin or if its value is less than or equal to 4.7 k $\Omega$ , then the UFP VDO data capability bit is set to 1, which correlates to the port being data capable. If the value of the pull-up resistor is 50 k $\Omega$ , then the UFP VDO data capability bit is set to 0, which correlates to the port not being data capable. |

| 11         | VDC_OUT     | Connect this pin to the output of the PFETs controlled by the VBUS_FET_EN. This is used for monitoring the VBUS output. This is the power output of the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12         | HPI_SDA     | This is an I <sup>2</sup> C slave interface provided for a host processor to control and monitor the EZ-PD BCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13         | HPI_SCL     | device. For more details, refer to the HPI Specification for EZ-PD BCR device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14         | CC2         | Communication Channel 2 pin used to negotiate a voltage/current with the attached adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15         | CC1         | Communication Channel 1 pin used to negotiate a voltage/current with the attached adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16         | D-          | Leave this pin unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17         | D+          | Leave this pin unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18         | VBUS_IN     | Connect to VBUS of USB Type-C connector. Used to supply power to the EZ-PD BCR device and monitor incoming voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19         | GND         | System Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20         | DNU1        | Leave this pin unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21         | DNU2        | Leave this pin unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 22         | VSS         | Ground pin, connect to USB Type-C connector GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 1. EZ-PD BCR Pin Descriptions (continued)

| 24-Pin QFN | Pin Name | Description                                                                |  |  |  |  |  |

|------------|----------|----------------------------------------------------------------------------|--|--|--|--|--|

| 23         | VDDD     | Output of internal 3.3-V regulator. Connect 1 μF and 2x 100-nF capacitors. |  |  |  |  |  |

| 24         | VCCD     | Output of internal 1.8-V regulator. Connect a 1-µF decoupling capacitor.   |  |  |  |  |  |

| -          | EPAD     | Ground                                                                     |  |  |  |  |  |

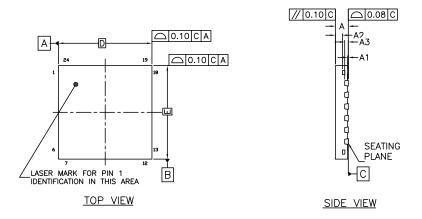

Figure 2. Pinout of 24-QFN Package (Top View)

## **Application Overview**

Figure 3 shows the EZ-PD BCR-based application diagram using the 24-pin QFN part. It has three main parts: USB Type-C receptacle to provide the input power to the application, the Power Subsystem used as the output power, and four sets of resistor divider networks to select the desired output voltage and current values.

The 'Fault' pin is used to indicate any voltage faults. When a fault condition is enabled, the output voltage of this application will go down to 0V and the EZ-PD BCR device will attempt a protocol reset to recover from fault. For a detailed reference schematic, refer to the CY4533 EZ-PD BCR EVK schematic.

Type-C Receptacle Power Subsystem \_ 1μF 10K£ 3.3µF 49.9KO SAFE PWR ≲ 49.9 KO 3.3V 1 KΩ ≶ ≤1 KΩ 1µF 0.1µF 3.3 V 23 2.2 KΩ 2.2 KΩ VBUS\_FET\_EN VDDD SAFE PWR EN 18 VBUS IN 11 VDC OUT 14 CC2 12 SOC HPI SDA 15 CC1 13 HPI\_SCI x <u>17</u> D+ x <u>16</u> 20 DNU1 D-CYPD3177-24LQXI 3.3 V 21 DNU2 4.7 KΩ 10 FLIP  $\sim$ HPI\_INT VBUS 24 VCCD GPIO\_1 1kΩ W uЕ 19.22 GND FAULT ISNK\_COARSE ISNK\_FINE VBUS\_MIN VBUS\_MAX 5 6 2 VDDIO VDDIO VDDIO VDDIO R5 < Śr₃ ≥r1 R7≤ R4 ≥ R2 ≥  $\gtrsim R6$ ≶r8

Notes

1. Refer to Table 2, Table 3, and Table 4 for values of these resistor divider networks.

2. FLIP bin is in LOW state when TypeC Plug is upside-up, and in H-Z state when upside-down. 3. Use a 50- $\alpha$  resistor on the FLIP pin to set the UFP VDO data capability bit to 0.

The four sets of resistor divider networks are used to determine the voltage and current range that the EZ-PD BCR device will negotiate with the USB Type-C power adapter. Table 2, Table 3, and Table 4 show the values of pull-up and pull-down resistors on each pin applicable for a desired VBUS\_MIN, VBUS\_MAX, ISNK\_COARSE or ISNK\_FINE value.

**Note 1:** If VBUS\_MIN is more than VBUS\_MAX, the setting on VBUS\_MAX is used as both minimum and maximum VBUS setting for the system.

**Note 2:** EZ-PD BCR device does not monitor the current on VBUS\_IN and enforce it within ISNK limits. It is the responsibility of the system to not consume more current than what the power adapter can provide.

**Note 3:** VBUS\_MIN and VBUS\_MAX can be set to the same value to select one specific voltage level from the Type-C power adapter. **Note 4:** Ensure that the board layout design does not inject any noise into the VBUS\_MIN, VBUS\_MAX, ISNK\_COARSE, ISNK\_FINE pins.

| Table 2. | Resistor | Divider | Values <sup>•</sup> | for Minimum | or Maximum | Voltage Reg | quested on VBUS |

|----------|----------|---------|---------------------|-------------|------------|-------------|-----------------|

|          |          |         |                     |             |            |             |                 |

| Voltage Requested<br>(V) | Resistor Ratio Relative<br>to VDDD = 3.3 V | Suggested Pull-up<br>Resistor value (kΩ) | Suggested Pull-down<br>Resistor value (kΩ) | Voltage Range on Pin<br>(mV) |

|--------------------------|--------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------|

| 5                        | 0/6                                        | Open                                     | 0                                          | 0–248                        |

| 9                        | 1/6                                        | 5.1                                      | 1                                          | 249–786                      |

| 12                       | 2/6                                        | 5.1                                      | 2.4                                        | 787–1347                     |

| 15                       | 3/6                                        | 5.1                                      | 5.1                                        | 1348–1920                    |

| 19                       | 4/6                                        | 5.1                                      | 10                                         | 1921–2778                    |

| 20                       | ≥ 5/6                                      | 0                                        | Open                                       | ≥ 2779                       |

Table 3. Resistor Divider Values for Coarse Setting on Operating Current (For VDDD = 3.3 V)

| Operating Current<br>Requested for Coarse<br>Setting (A) | Resistor Ratio Relative<br>to VDDD = 3.3 V | Suggested Pull-up Resistor Value (k $\Omega$ ) | Suggested Pull-down<br>Resistor Value (kΩ) | Voltage Range on Pin<br>(mV) |

|----------------------------------------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------|------------------------------|

| 0                                                        | 0/6                                        | Open                                           | 0                                          | 0–248                        |

| 1                                                        | 1/6                                        | 5.1                                            | 1                                          | 249–786                      |

| 2                                                        | 2/6                                        | 5.1                                            | 2.4                                        | 787–1347                     |

| 3                                                        | 3/6                                        | 5.1                                            | 5.1                                        | 1348–1920                    |

| 4                                                        | 4/6                                        | 5.1                                            | 10                                         | 1921–2778                    |

| 5                                                        | ≥ 5/6                                      | 0                                              | Open                                       | ≥ 2779                       |

| Operating Current<br>Requested for Fine<br>Setting (A) | Resistor Ratio Relative<br>to VDDD = 3.3 V | Suggested Pull-up Resistor Value (k $\Omega$ ) | Suggested Pull-down<br>Resistor Value (kΩ) | Voltage Range on Pin<br>(mV) |

|--------------------------------------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------|------------------------------|

| +0                                                     | 0/6                                        | Open                                           | 0                                          | 0–248                        |

| +250                                                   | 1/6                                        | 5.1                                            | 1                                          | 249–786                      |

| +500                                                   | 2/6                                        | 5.1                                            | 2.4                                        | 787–1347                     |

| +750                                                   | 3/6                                        | 5.1                                            | 5.1                                        | 1348–1920                    |

| +900                                                   | ≥ 4/6                                      | 0                                              | Open                                       | ≥ 1921                       |

#### FAULT Pin Behavior

FAULT is driven to Logic HIGH if at least one of the following conditions is met:

Type-C power adapter cannot supply a voltage within VBUS\_MIN and VBUS\_MAX settings and/or supply a current of at least ISNK\_COARSE + ISNK\_FINE value.

■ Voltage on VBUS\_IN is 20% below the VBUS\_MIN setting or 20% above the VBUS\_MAX setting.

FAULT is driven to Logic LOW otherwise.

#### SAFE\_PWR\_EN pin Behavior

SAFE\_PWR\_EN is a PFET gate driver that can be used to provide power to the system when an incompatible power adapter is attached to the system. SAFE\_PWR\_EN is driven to 0V when the Type-C power adapter cannot supply a voltage within VBUS\_MIN and VBUS\_MAX settings and/or supply a current of at least ISNK\_COARSE + ISNK\_FINE value. In this case, the EZ-PD BCR device negotiates for a 5V@ I<sub>SNK</sub> contract with the USB-PD Power Adapter when possible.

SAFE\_PWR\_EN pin is left floating (High-Z) in all other conditions.

#### VBUS\_FET\_EN pin Behavior

The VBUS\_FET\_EN pin is a PFET gate driver that drives to either 0 V or VBUS\_IN depending on the state of the Type-C connection. Contact Cypress Technical Support for more details on how to use this pin for specific applications.

## **Electrical Specifications**

#### **Absolute Maximum Ratings**

#### Table 5. Absolute Maximum Ratings

| Parameter                   | Description                                                                | Min   | Тур | Max                                       | Unit | Details/Conditions                                                          |

|-----------------------------|----------------------------------------------------------------------------|-------|-----|-------------------------------------------|------|-----------------------------------------------------------------------------|

| V <sub>BUS_MAX</sub>        | Max supply voltage relative to V <sub>SS</sub> on VBUS_IN and VDC_OUT pins |       |     | V                                         |      |                                                                             |

| V <sub>DDD_MAX</sub>        | Max supply voltage relative to $V_{SS}$                                    | -     | -   | 6                                         | V    |                                                                             |

| V <sub>CC_PIN_ABS</sub>     | Max voltage on CC1, CC2 pins                                               | -     | -   | 22 <sup>[1]</sup>                         | V    | Absolute max                                                                |

| V <sub>GPIO_ABS</sub>       | GPIO voltage                                                               | -0.5  | -   | V <sub>DDD</sub> +0.5                     | V    |                                                                             |

| I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                   | -25   | -   | 25                                        | mA   |                                                                             |

| I <sub>GPIO_injection</sub> | GPIO injection current. Max for V <sub>III</sub> > 0.5                     |       | mA  | Absolute max, current<br>injected per pin |      |                                                                             |

| V <sub>GPIO_OVT_ABS</sub>   | OVT GPIO voltage                                                           | -0.5  | -   | 6                                         | V    | Applicable to pins HPI_INT and GPIO_1                                       |

| ESD_HBM                     | Electrostatic discharge human body model                                   | 2200  | _   | -                                         | V    | -                                                                           |

| ESD_CDM                     | Electrostatic discharge charged device model                               | 500   | _   | -                                         | V    | -                                                                           |

| LU                          | Pin current for latch-up                                                   | -100  | -   | 100                                       | mA   | -                                                                           |

| ESD_IEC_CON                 | Electrostatic discharge IEC61000-4-2                                       | 8000  | _   | -                                         | V    | Contact discharge on CC1,<br>CC2, VBUS_IN, HPI_SDA<br>and HPI_SCL pins      |

| ESD_IEC_AIR                 | Electrostatic discharge IEC61000-4-2                                       | 15000 | _   | _                                         | V    | Air discharge for D+, D-, CC1,<br>CC2, VBUS_IN, HPI_SDA<br>and HPI_SCL pins |

#### **Device-Level Specifications**

All specifications are valid for –40  $^\circ C \leq T_A \leq 105^\circ C$  and  $T_J \leq 120^\circ C,$  except where noted.

#### Table 6. DC Specifications

| Spec ID     | Parameter           | Description                                                     | Min | Тур | Max  | Unit | Details/Conditions                                     |

|-------------|---------------------|-----------------------------------------------------------------|-----|-----|------|------|--------------------------------------------------------|

| SID.PWR#2   | V <sub>DDD</sub>    | Power supply input voltage                                      | 2.7 | -   | 5.5  | V    | Sink mode, $-40^{\circ}C \le T_A \le 105^{\circ}C$ .   |

| SID.PWR#2_A | V <sub>DDD</sub>    | Power supply input voltage                                      | 3.0 | -   | 5.5  | V    | Source mode, $-40^{\circ}C \le T_A \le 105^{\circ}C$ . |

| SID.PWR#3   | V <sub>BUS_IN</sub> | Power supply input voltage                                      | 3.0 | -   | 24.5 | V    | $-40~^\circ C \leq T_A \leq 105^\circ C.$              |

| SID.PWR#5   | V <sub>CCD</sub>    | Output voltage for core Logic                                   | -   | 1.8 | -    | V    | -                                                      |

| SID.PWR#13  | C <sub>exc</sub>    | Power supply decoupling capacitor for V <sub>DDD</sub>          | 0.8 | 1   | -    | μF   | X5R ceramic or better                                  |

| SID.PWR#14  | C <sub>exv</sub>    | Power supply decoupling<br>capacitor for VBUS_IN_DISH-<br>CARGE | _   | 0.1 | -    | μF   | X5R ceramic or better                                  |

Note

1. As per USB PD specification, maximum allowed VBUS = 21.5 V.

#### Table 6. DC Specifications (continued)

| Spec ID              | Parameter                                                                                        | Parameter Description                                                  |      | Тур | Max | Unit | Details/Conditions                                                                                                                                                    |  |  |

|----------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Active Mode. Ty      | Active Mode. Typical values measured at $V_{DDD}$ = 5.0 V or $V_{BUS}$ = 5.0 V and $T_A$ = 25°C. |                                                                        |      |     |     |      |                                                                                                                                                                       |  |  |

| SID.PWR#8            | I <sub>DD_A</sub>                                                                                | Supply current from V <sub>BUS</sub> or<br>V <sub>DDD</sub>            | _    | 10  | _   | mA   | $V_{DDD} = 5 V OR V_{BUS} = 5 V,$<br>$T_A = 25^{\circ}C. CC1/CC2 in Tx or Rx,$<br>no I/O sourcing current, 2 SCBs at<br>1 Mbps, EA/ADC/CSA/UVOV ON,<br>CPU at 24 MHz. |  |  |

| Sleep Mode. Ty       | pical values meas                                                                                | ured at $V_{DD}$ = 3.3 V and $T_A$ = 2                                 | 5°C. |     |     |      |                                                                                                                                                                       |  |  |

| SID25A               | I <sub>DD_S</sub>                                                                                | CC, I <sup>2</sup> C, WDT wakeup on.<br>IMO at 24 MHz.                 | -    | 3   | -   | mA   | V <sub>DDD</sub> = 3.3 V, T <sub>A</sub> = 25°C,<br>All blocks except CPU are on, CC<br>IO on, EA/ADC/CSA/UVOV On.                                                    |  |  |

| Deep Sleep Mo        | de. Typical values                                                                               | measured at T <sub>A</sub> = 25°C.                                     |      |     |     |      |                                                                                                                                                                       |  |  |

| SID_P-<br>B_DS_A_SNK | I <sub>DD_PB_DS_A_SNK</sub>                                                                      | V <sub>BUS</sub> 4.0 to 24.5 V.<br>CC, I <sup>2</sup> C, WDT Wakeup on | _    | 500 | _   | μΑ   | For sink applications,<br>V <sub>BUS</sub> = 24.5 V, T <sub>A</sub> = 25 °C, Part is in<br>deep sleep. Attached, CC I/O on,<br>ADC/CSA/UVOV on.                       |  |  |

### Table 7. AC Specifications (Guaranteed by Characterization)

| Spec ID     | Parameter              | Description                                               | Min | Тур | Мах | Unit | Details/Conditions |

|-------------|------------------------|-----------------------------------------------------------|-----|-----|-----|------|--------------------|

| SID.PWR#17  | T <sub>SLEEP</sub>     | Wakeup from sleep mode                                    | -   | 0   | -   | μs   | -                  |

| SID.PWR#18  | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep<br>mode                            | -   | -   | 35  | μs   | _                  |

| SYS.FES#1   | T_ <sub>PWR_RDY</sub>  | Power-up to "Ready to accept I <sup>2</sup> C/CC command" | -   | 5   | 25  | ms   | _                  |

| SID.PWR#18A | T <sub>POR_HIZ_T</sub> | Power-on I/O Initialization<br>Time                       | -   | 3   | Ι   | ms   | _                  |

I/O

## Table 8. I/O DC Specifications

| Spec ID     | Parameter            | Description                               | Min                     | Тур | Max                  | Unit | Details/Conditions                                                                                                           |

|-------------|----------------------|-------------------------------------------|-------------------------|-----|----------------------|------|------------------------------------------------------------------------------------------------------------------------------|

| SID.GIO#37  | V <sub>IH_CMOS</sub> | Input voltage HIGH threshold              | $0.7 \times V_{DDD}$    | -   | -                    | V    | CMOS input                                                                                                                   |

| SID.GIO#38  | V <sub>IL_CMOS</sub> | Input voltage LOW threshold               | -                       | -   | $0.3 \times V_{DDD}$ | V    | CMOS input                                                                                                                   |

| SID.GIO#33  | V <sub>OH_3V</sub>   | Output voltage HIGH level                 | V <sub>DDD</sub> -0.6   | _   | _                    | V    | I <sub>OH</sub> = 4 mA at 3-V<br>V <sub>DDD</sub>                                                                            |

| SID.GIO#36  | V <sub>OL_3V</sub>   | Output voltage LOW level                  | _                       | _   | 0.6                  | V    | I <sub>OL</sub> = 10 mA at 3-V<br>V <sub>DDD</sub>                                                                           |

| SID.GIO#16  | IIL                  | Input leakage current<br>(absolute value) | -                       | -   | 2                    | nA   | +25°C T <sub>A</sub> , 3-V V <sub>DDD</sub>                                                                                  |

| SID.GIO#17  | C <sub>PIN_A</sub>   | Max pin capacitance                       | -                       | -   | 22                   | pF   | Capacitance on D+,<br>D- pins. Guaranteed<br>by characterization.                                                            |

| SID.GIO#17A | C <sub>PIN</sub>     | Max pin capacitance                       | -                       | 3   | 7                    | pF   | –40°C to +85°C T <sub>A</sub> ,<br>All V <sub>DDD</sub> , all other<br>I/O <sub>S</sub> . Guaranteed by<br>characterization. |

| SID.GIO#44  | V <sub>HYSCMOS</sub> | Input hysteresis CMOS                     | 0.05 × V <sub>DDD</sub> | _   | -                    | mV   | V <sub>DDD</sub> < 4.5 V.<br>Guaranteed by<br>characterization.                                                              |

#### Table 8. I/O DC Specifications (continued)

| Spec ID    | Parameter             | Description                                              | Min | Тур | Max   | Unit | Details/Conditions                 |

|------------|-----------------------|----------------------------------------------------------|-----|-----|-------|------|------------------------------------|

| SID69      | I <sub>DIODE</sub>    | Current through protection diode to $V_{DDD}/V_{SS}$     | -   | -   | 100   | μA   | Guaranteed by<br>design.           |

| SID.GIO#45 | I <sub>TOT_GPIO</sub> | Maximum total sink chip current                          | -   | -   | 85    | mA   | Guaranteed by<br>design.           |

| OVT        |                       |                                                          |     |     |       |      |                                    |

| SID.GIO#46 | I <sub>IHS</sub>      | Input current when Pad > V <sub>DDD</sub> for OVT inputs | _   | _   | 10.00 | μA   | Per I <sup>2</sup> C specification |

#### Table 9. I/O AC Specifications

(Guaranteed by Characterization)

| Spec ID | Parameter          | Description                   | Min | Тур | Мах | Unit | Details/Conditions                                 |

|---------|--------------------|-------------------------------|-----|-----|-----|------|----------------------------------------------------|

| SID70   | T <sub>RISEF</sub> | Rise time in Fast Strong mode | 2   | -   | 12  | ns   | 3.3-V V <sub>DDD</sub> , C <sub>load</sub> = 25 pF |

| SID71   | T <sub>FALLF</sub> | Fall time in Fast Strong mode | 2   | 1   | 12  | ns   | 3.3-V V <sub>DDD</sub> , C <sub>load</sub> = 25 pF |

#### Table 10. HPI Pins DC Specifications (Applicable to pins HPI\_SDA and HPI\_SCL only)

(Guaranteed by Characterization)

| Spec ID          | Parameter        | Description                                                    | Min  | Тур | Max | Unit | Details/Conditions                                                           |

|------------------|------------------|----------------------------------------------------------------|------|-----|-----|------|------------------------------------------------------------------------------|

| SID.GPIO_20VT#4  | GPIO_20VT_I_LU   | GPIO_20VT Latch up current limits                              | -140 | Ι   | 140 | mA   | Max / min current in to any<br>input or output, pin-to-pin,<br>pin-to-supply |

| SID.GPIO_20VT#5  | GPIO_20VT_RPU    | GPIO_20VT Pull-up resistor value                               | 1    | Ι   | 25  | kΩ   | +25°C T <sub>A</sub> , 1.4 V to<br>GPIO_20VT_Voh(min)                        |

| SID.GPIO_20VT#6  | GPIO_20VT_RPD    | GPIO_20VT Pull-down<br>resistor value                          | 2.5  | -   | 20  | kΩ   | +25°C T <sub>A</sub> , 1.4-V to V <sub>DDD</sub>                             |

| SID.GPIO_20VT#16 | GPIO_20VT_IIL    | GPIO_20VT Input leakage<br>current (absolute value)            | -    | -   | 2   | nA   | +25°C T <sub>A</sub> , 3-V V <sub>DDD</sub>                                  |

| SID.GPIO_20VT#17 | GPIO_20VT_CPIN   | GPIO_20VT pin capacitance                                      | 15   | -   | 25  | pF   | –40°C to +85°C T <sub>A</sub> , All<br>V <sub>DDD</sub> , F = 1 MHz          |

| SID.GPIO_20VT#36 | GPIO_20VT_Vol    | GPIO_20VT Output Voltage<br>low level                          | -    | -   | 0.4 | V    | I <sub>OL</sub> = 2 mA                                                       |

| SID.GPIO_20VT#69 | GPIO_20VT_IDIODE | GPIO_20VT Current through protection diode to $V_{DDD}/V_{SS}$ | _    | _   | 100 | μA   | -                                                                            |

#### Table 11. HPI Pins AC Specifications (Applicable to pins HPI\_SDA and HPI\_SCL only)

(Guaranteed by Characterization)

| Spec ID          | Parameter        | Description                                | Min | Тур | Max | Unit | Details/Conditions                               |

|------------------|------------------|--------------------------------------------|-----|-----|-----|------|--------------------------------------------------|

| SID.GPIO_20VT#70 | GPIO_20VT_TriseF | GPIO_20VT Rise time in<br>Fast Strong Mode | 1   | -   | 45  | ns   | All V <sub>DDD</sub> , C <sub>load</sub> = 25 pF |

| SID.GPIO_20VT#71 | GPIO_20VT_TfallF | GPIO_20VT Fall time in Fast<br>Strong Mode | 2   | _   | 15  | ns   | All V <sub>DDD</sub> , C <sub>load</sub> = 25 pF |

#### **Digital Peripherals**

The following specifications apply to the Timer/Counter/PWM peripherals in the Timer mode.

#### βC

#### Table 12. Fixed I<sup>2</sup>C DC Specifications

(Guaranteed by Characterization)

| Spec ID | Parameter         | Description                                 | Min | Тур | Max | Unit | Details/Conditions |

|---------|-------------------|---------------------------------------------|-----|-----|-----|------|--------------------|

| SID149  | I <sub>I2C1</sub> | Block current consumption at 100 kHz        | -   | -   | 100 | μA   | -                  |

| SID150  | I <sub>I2C2</sub> | Block current consumption at 400 kHz        | -   | -   | 135 | μA   | -                  |

| SID152  | I <sub>I2C4</sub> | I <sup>2</sup> C enabled in Deep Sleep mode | -   | 1.4 | -   | μA   | _                  |

#### Table 13. Fixed I<sup>2</sup>C AC Specifications

(Guaranteed by Characterization)

| Spec ID | Parameter         | Description | Min | Тур | Max | Unit | Details/Conditions |

|---------|-------------------|-------------|-----|-----|-----|------|--------------------|

| SID153  | F <sub>I2C1</sub> | Bit rate    | -   | -   | 400 | kbps | -                  |

#### System Resources

#### Power-on-Reset (POR) with Brown Out SWD Interface

#### Table 14. Imprecise Power On Reset (PRES) (Guaranteed by Characterization)

| Spec ID | Parameter             | Description                              | Min  | Тур | Max  | Unit | Details/Conditions |

|---------|-----------------------|------------------------------------------|------|-----|------|------|--------------------|

| SID185  | V <sub>RISEIPOR</sub> | Power-on Reset (POR) rising trip voltage | 0.80 | -   | 1.50 | V    | _                  |

| SID186  | V <sub>FALLIPOR</sub> | POR falling trip voltage                 | 0.70 | -   | 1.4  | V    | -                  |

#### Table 15. Precise Power On Reset (POR)

(Guaranteed by Characterization)

| Spec ID | Parameter              | Description                                                  | Min  | Тур | Мах  | Unit | Details/Conditions |

|---------|------------------------|--------------------------------------------------------------|------|-----|------|------|--------------------|

| SID190  |                        | Brown-out Detect (BOD) trip voltage<br>in active/sleep modes | 1.48 | -   | 1.62 | V    | _                  |

| SID192  | V <sub>FALLDPSLP</sub> | BOD trip voltage in Deep Sleep mode                          | 1.1  | -   | 1.5  | V    | -                  |

#### Table 16. USB PD DC Specifications

| Spec ID  | Parameter  | Description                                                    | Min  | Тур | Max  | Unit | Details/Conditions                                         |

|----------|------------|----------------------------------------------------------------|------|-----|------|------|------------------------------------------------------------|

| SID.PD.4 | Rd         | UFP CC termination                                             | 4.59 | 5.1 | 5.61 | kΩ   | _                                                          |

| SID.PD.5 | Rd_DB      | UFP (Power Bank) Dead Battery CC<br>Termination on CC1 and CC2 | 4.08 | 5.1 | 6.12 | kΩ   | All supplies forced to 0V and 1.32 V applied at CC1 or CC2 |

| SID.PD.6 | Vgndoffset | Ground offset tolerated by BMC receiver                        | -500 | Ι   | 500  | mV   | Relative to the remote BMC transmitter                     |

#### Gate Driver Specifications

## Table 17. Gate Driver DC Specifications

| Spec ID   | Parameter        | Description                                      | Min  | Тур   | Max  | Unit | Details/Conditions                                                           |

|-----------|------------------|--------------------------------------------------|------|-------|------|------|------------------------------------------------------------------------------|

| SID.GD.1  | R <sub>PD</sub>  | Pull-down resistance                             | _    | _     | 3    | kΩ   | Applicable on<br>VBUS_P_CTRL and<br>VBUS_C_CTRL to turn ON<br>external PFET. |

| SID.GD.2  | R <sub>PU</sub>  | Pull-up resistance                               | -    | -     | 4    | kΩ   | Applicable on<br>VBUS_P_CTRL to turn OFF<br>external PFET.                   |

| SID.GD.3  | I <sub>PD0</sub> | Pull-down current sink at drive<br>strength of 1 | 25   | -     | 75   | μA   |                                                                              |

| SID.GD.4  | I <sub>PD1</sub> | Pull-down current sink at drive<br>strength of 2 | 50   | -     | 150  | μA   | l mode (ourrent mode) pull                                                   |

| SID.GD.5  | I <sub>PD2</sub> | Pull-down current sink at drive<br>strength of 4 | 140  | -     | 300  | μA   | I-mode (current mode) pull<br>down at 5 V.<br>Applicable on                  |

| SID.GD.6  | I <sub>PD3</sub> | Pull-down current sink at drive strength of 8    | 280  | -     | 580  | μA   | VBUS_P_CTRL and<br>VBUS_C_CTRL to turn ON<br>external PFET.                  |

| SID.GD.7  | I <sub>PD4</sub> | Pull-down current sink at drive strength of 16   | 560  | -     | 1200 | μA   |                                                                              |

| SID.GD.8  | I <sub>PD5</sub> | Pull-down current sink at drive strength of 32   | 1120 | -     | 2300 | μA   |                                                                              |

| SID.GD.9  | I_leak_p1        | Pin leakage on VBUS_P_CTRL                       | -    | 0.003 | -    | μA   | +25°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BUS</sub>       |

| SID.GD.10 | I_leak_c1        | Pin leakage on VBUS_C_CTRL                       | _    | 0.003 | _    | μA   | +25°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BU</sub>        |

| SID.GD.11 | I_leak_p2        | Pin leakage on VBUS_P_CTRL                       | _    | _     | 2    | μA   | +85°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BU</sub>        |

| SID.GD.12 | I_leak_c2        | Pin leakage on VBUS_C_CTRL                       | -    | -     | 2    | μA   | +85°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BU</sub>        |

| SID.GD.13 | I_leak_p3        | Pin leakage on VBUS_P_CTRL                       | _    | _     | 7    | μA   | +125°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BU</sub>       |

| SID.GD.14 | I_leak_c3        | Pin leakage on VBUS_C_CTRL                       | -    | -     | 7    | μA   | +125°C T <sub>J</sub> , 5-V V <sub>DDD</sub> ,<br>20-V V <sub>BU</sub>       |

#### Table 18. Gate Driver AC Specifications

(Guaranteed by Characterization)

| Spec ID   | Parameter                | Description                                     | Min | Тур | Мах | Unit | Details/Conditions                                                                                                                                          |

|-----------|--------------------------|-------------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SID.GD.15 | T <sub>PD1</sub>         | Pull down delay on SAFE_PWR_EN                  | _   | _   | 2   | μs   | Cload = 2 nF,<br>Delay to VBUS $-1.5$ V from<br>initiation of falling edge,<br>VBUS = 5 V to 20 V,<br>50 k $\Omega$ tied between<br>VBUS_C_CTRL and VBUS    |

| SID.GD.16 | T <sub>r_discharge</sub> | Discharge rate of output node on<br>SAFE_PWR_EN | _   | -   | 5   | V/µs | 80% to 20%,<br>50 kΩ tied between<br>VBUS_C_CTRL and VBUS,<br>Cload = 2 nF, Vinitial = 24 V                                                                 |

| SID.GD.17 | T <sub>PD2</sub>         | Pull down delay on VBUS_FET_EN                  | -   | -   | 2   | μs   | Cload = 2 nF,<br>Delay to VBUS –1.5 V from<br>initiation of falling edge,<br>$V_{BUS} = 5 V$ to 20 V,<br>50 k $\Omega$ tied between<br>VBUS_C_CTRL and VBUS |

| SID.GD.18 | T <sub>PU</sub>          | Pull up delay on VBUS_FET_EN                    | _   | _   | 18  | μs   | Cload = 2 nF,<br>Delay to VBUS-1.5 V from<br>initiation of falling edge,<br>VBUS = 5 V to 20 V,<br>50 k $\Omega$ tied between<br>VBUS_C_CTRL and VBUS       |

| SID.GD.19 | SR <sub>PU</sub>         | Output slew rate on VBUS_FET_EN                 | _   | _   | 5   | V/µs | Cload = 2 nF, 20% to 80% of<br>VBUS_P_CTRL range                                                                                                            |

| SID.GD.20 | SR <sub>PD</sub>         | Output slew rate on VBUS_FET_EN                 | _   | _   | 5   | V/µs | Cload = 2 nF, 80% to 20% of<br>VBUS_P_CTRL range                                                                                                            |

#### Table 19. VBUS Discharge Specifications

| Spec ID          | Parameter           | Description                                                   | Min  | Тур | Max | Unit | Details/Conditions                                                             |  |

|------------------|---------------------|---------------------------------------------------------------|------|-----|-----|------|--------------------------------------------------------------------------------|--|

| SID.VBUS.DISC.6  | 11                  | 20-V NMOS ON current for DS = 1                               | 0.15 | -   | 1   | mA   |                                                                                |  |

| SID.VBUS.DISC.7  | 12                  | 20-V NMOS ON current for DS = 2                               | 0.4  | -   | 2   | mA   |                                                                                |  |

| SID.VBUS.DISC.8  | 14                  | 20-V NMOS ON current for DS = 4                               | 0.9  | -   | 4   | mA   | Measured at 0.5 V                                                              |  |

| SID.VBUS.DISC.9  | 18                  | 20-V NMOS ON current for DS = 8                               | 2    | -   | 8   | mA   |                                                                                |  |

| SID.VBUS.DISC.10 | 116                 | 20-V NMOS ON current for DS = 16                              | 4    | -   | 10  | mA   |                                                                                |  |

| SID.VBUS.DISC.11 | VBUS_Stop<br>_Error | Error percentage of final V <sub>BUS</sub> value from setting | Ι    | _   | 10  |      | When V <sub>BUS</sub> is discharged to 5 V.<br>Guaranteed by Characterization. |  |

| Spec ID      | Parameter           | Description                 | Min   | Тур | Max   | Unit | Details/Conditions                                     |

|--------------|---------------------|-----------------------------|-------|-----|-------|------|--------------------------------------------------------|

| SID.DC.VR.1  | $V_{IN_3}$          | V(pad_in) at 3-V target     | 2.85  | 3   | 3.15  | V    | Active mode shunt regulator at 3 V with bandgap        |

| SID.DC.VR.2  | $V_{IN_5}$          | V(pad_in) at 5-V target     | 4.75  | 5   | 5.25  | V    | Active mode shunt regulator at 5 V                     |

| SID.DC.VR.3  | V_IN_9              | V(pad_in) at 9-V target     | 8.55  | 9   | 9.45  | V    | Active mode shunt regulator at<br>9 V                  |

| SID.DC.VR.4  | V_IN_15             | V(pad_in) at 15-V target    | 14.25 | 15  | 15.75 | V    | Active mode shunt regulator at 15 V                    |

| SID.DC.VR.5  | V_IN_20             | V(pad_in) at 20-V target    | 19    | 20  | 21    | V    | Active mode shunt regulator at 20 V                    |

| SID.DC.VR.6  | V_IN_3_DS           | V(pad_in) at 3-V target     | 2.7   | 3   | 3.3   | V    | Deep Sleep mode shunt<br>regulator at 3 V with bandgap |

| SID.DC.VR.7  | V_IN_5_DS           | V(pad_in) at 5-V target     | 4.5   | 5   | 5.5   | V    | Deep Sleep mode shunt<br>regulator at 5 V              |

| SID.DC.VR.8  | V_IN_9_DS           | V(pad_in) at 9-V target     | 8.1   | 9   | 9.1   | V    | Deep Sleep mode shunt<br>regulator at 9 V              |

| SID.DC.VR.9  | V_IN_15_DS          | V(pad_in) at 15-V target    | 13.5  | 15  | 16.5  | V    | Deep Sleep mode shunt<br>regulator at 15 V             |

| SID.DC.VR.10 | V_IN_20_DS          | V(pad_in) at 20-V target    | 18    | 20  | 22    | V    | Deep Sleep mode shunt<br>regulator at 20 V             |

| SID.DC.VR.11 | I <sub>KA_OFF</sub> | Off-state cathode current   | —     | -   | 10    | μA   | -                                                      |

| SID.DC.VR.12 | I <sub>KA_ON</sub>  | Current through cathode pin | -     | -   | 10    | mA   | -                                                      |

#### Table 20. Voltage (VBUS) Regulation DC Specifications

#### Table 21. VBUS Short Protection Specifications

| Spec ID | Parameter | Description                                                               | Min | Тур | Max | Unit | Details/Conditions              |

|---------|-----------|---------------------------------------------------------------------------|-----|-----|-----|------|---------------------------------|

|         |           | Short-to-VBUS system-side<br>clamping voltage on the<br>CC/P2.2/P2.3 pins | _   | 9   | _   | V    | Guaranteed by Characterization. |

#### Table 22. VBUS DC Regulator Specifications

| Spec ID    | Parameter      | Description                   | Min  | Тур | Max  | Unit | Details/Conditions |

|------------|----------------|-------------------------------|------|-----|------|------|--------------------|

| SID.VREG.2 | VBUS<br>DETECT | VBUS detect threshold voltage | 1.08 | -   | 2.62 | V    | -                  |

#### Table 23. VBUS AC Regulator Specifications

| Spec ID    | Parameter          | Description                                         | Min | Тур | Max | Unit | Details/Conditions              |

|------------|--------------------|-----------------------------------------------------|-----|-----|-----|------|---------------------------------|

| SID.VREG.3 | T <sub>start</sub> | Total startup time for the regulator supply outputs | Ι   | Ι   | 200 | μs   | Guaranteed by Characterization. |

#### Analog to Digital Converter (Used for Determining VBUS\_MIN,

#### Table 24. ADC DC Specifications (Guaranteed by Characterization)

| Spec ID    | Parameter             | Description                                         | Min  | Тур | Max  | Unit | Details/Conditions                          |

|------------|-----------------------|-----------------------------------------------------|------|-----|------|------|---------------------------------------------|

| SID.ADC.1  | Resolution            | ADC resolution                                      | -    | 8   | -    | Bits | -                                           |

| SID.ADC.2  | INL                   | Integral non-linearity                              | -2.5 | Ι   | 2.5  | LSB  | Reference voltage generated from VDDD       |

| SID.ADC.2A | INL                   | Integral non-linearity                              | -1.5 | _   | 1.5  | LSB  | Reference voltage generated from<br>bandgap |

| SID.ADC.3  | DNL                   | Differential non-linearity                          | -2.5 | _   | 2.5  | LSB  | Reference voltage generated from VDDD       |

| SID.ADC.3A | DNL                   | Differential non-linearity                          | -1.5 | _   | 1.5  | LSB  | Reference voltage generated from<br>bandgap |

| SID.ADC.4  | Gain Error            | Gain error                                          | -1.5 | -   | 1.5  | LSB  | -                                           |

| SID.ADC.6  | V <sub>REF_ADC2</sub> | ADC reference voltage when generated from band gap. | 1.96 | 2.0 | 2.04 | V    | Reference voltage generated from<br>bandgap |

### VBUS\_MAX, ISNK\_COARSE, ISNK\_FINE Values)

#### Table 25. ADC AC Specifications (Guaranteed by Design)

| Spec ID   | Parameter | Description                              | Min | Тур | Max | Unit | Details/Conditions |

|-----------|-----------|------------------------------------------|-----|-----|-----|------|--------------------|

| SID.ADC.7 | SLEW_Max  | Rate of change of sampled voltage signal | _   | _   | 3   | V/ms | -                  |

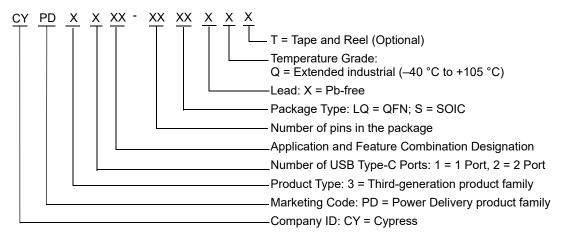

## **Ordering Information**

Table 26 lists the EZ-PD BCR part numbers and features.

#### Table 26. EZ-PD BCR Ordering Information

| MPN             | Application                                      | Termination<br>Resistor            | Role | Package Type | Si ID |

|-----------------|--------------------------------------------------|------------------------------------|------|--------------|-------|

| CYPD3177-24LQXQ | Barrel Connector Replacement or Generic UFP Sink | R <sub>D</sub> , R <sub>D-DB</sub> | UFP  | 24-Pin QFN   | 2004  |

#### **Ordering Code Definitions**

## Packaging

#### Table 27. Package Characteristics

| Parameter       | Description                      | Conditions          | Min | Тур | Max   | Unit |

|-----------------|----------------------------------|---------------------|-----|-----|-------|------|

| T <sub>A</sub>  | Operating ambient temperature    | Extended Industrial | -40 | 25  | 105   | °C   |

| Т <sub>Ј</sub>  | Operating junction temperature   | Extended Industrial | -40 | 25  | 120   | °C   |

| T <sub>JA</sub> | Package $\theta_{JA}$ (24-QFN)   | -                   | -   | -   | 19.98 | °C/W |

| T <sub>JC</sub> | Package θ <sub>JC</sub> (24-QFN) | _                   | _   | _   | 4.78  | °C/W |

#### Table 28. Solder Reflow Peak Temperature

| Package    | Maximum Peak Temperature | Maximum Time within<br>5 °C of Peak Temperature |

|------------|--------------------------|-------------------------------------------------|

| 24-pin QFN | 260 °C                   | 30 seconds                                      |

#### Table 29. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package    | MSL  |

|------------|------|

| 24-pin QFN | MSL3 |

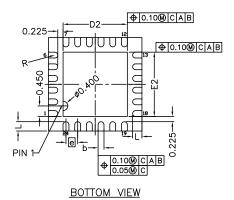

#### Figure 4. 24-pin QFN Package Outline

|        | DIMENSIONS |      |       |

|--------|------------|------|-------|

| SYMBOL | MIN.       | NOM. | MAX.  |

| А      | _          | —    | 0.60  |

| A1     | 0.00       | —    | 0.05  |

| A2     | —          | 0.40 | 0.425 |

| A3     | 0.152 REF  |      |       |

| b      | 0.18       | 0.25 | 0.30  |

| D      | 4.00 BSC   |      |       |

| D2     | 2.65       | 2.75 | 2.85  |

| E      | 4.00 BSC   |      |       |

| E2     | 2.65       | 2.75 | 2.85  |

| L      | 0.30       | 0.40 | 0.50  |

| е      | 0.50 BSC   |      |       |

| R      | 0.09       | —    | —     |

#### NOTES

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIE THICKNESS ALLOWABLE IS 0.305 mm MAXIMUM(.012 INCHES MAXIMUM)

- 3. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M -1994.

- 4. THE PIN #1 IDENTIFIER MUST BE PLACED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

- 5. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 6. PACKAGE WARPAGE MAX 0.08 mm.

- 7. APPLIED FOR EXPOSED PAD AND TERMINALS, EXCLUDE EMBEDDING PART OF EXPOSED PAD FROM MEASURING.

- 8. APPLIED ONLY TO TERMINALS.

- 9. JEDEC SPECIFICATION NO. REF. N.A.

002-16934 \*C

## Acronyms

#### Table 30. Acronyms Used in this Document

| Acronym                  | Description                                                                                                        |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| ADC                      | analog-to-digital converter                                                                                        |  |

| Arm <sup>®</sup>         | advanced RISC machine, a CPU architecture                                                                          |  |

| CC                       | configuration channel                                                                                              |  |