## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## **EZ-PD CCG6DF, CCG6SF**

# **USB Type-C Port Controller**

## **General Description**

EZ-PD™ CCG6DF and EZ-PD CCG6SF are dual-port and single-port USB Type-C controllers that comply with the latest USB Type-C and PD specifications. These devices provide a complete USB Type-C and USB-Power Delivery port control solution for PCs and notebooks. Both of these devices include a VBUS provider path load switch. These devices also contain a True Random Number Generator for authentication, a 32-bit, 48-MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M0 processor with 64-KB flash and 96-KB ROM, integrating a complete Type-C Transceiver including the Type-C termination resistors Rp, Rd, and dead battery Rd termination. CCG6DF is available in a 96-ball BGA package, whereas CCG6SF is available in 48-pin QFN package.

## **Applications**

- Notebooks and desktops

- Thunderbolt hosts, non-Thunderbolt hosts

#### **Features**

#### **USB-PD**

- Supports latest USB PD 3.0 specification

- Fast Role Swap (FRS)

- Extended Data Messaging

#### Type-C

- Integrated current sources for DFP<sup>[1]</sup> role (Rp)

- □ Default current at 900 mA

- □ 1.5 A

- **□3A**

- Integrated Rd resistor for UFP<sup>[2]</sup> role

- Integrated VCONN FETs to power EMCA cables

- Integrated dead battery termination

- Integrated high-voltage protection on CC and SBU pins to protect against accidental shorts to the VBUS pin on the Type-C connector

- Integrated pass through SBU Switch for 20-V protection

#### Mux

■ Integrated USB 2.0 Analog Mux for USB 2.0 HS and UART

#### Integrated Provider VBUS Load Switch

- VBUS Provider Switch (5 V/3A)

- Slew rate controlled turn-on on the VBUS provider path, tolerant to 24 V

- Configurable hardware-controlled VBUS overvoltage, undervoltage, overcurrent, short circuit, reverse current protection, and thermal shutdown

- VBUS high-side current sense amplifier capable of measuring current across 5-m $\Omega$  series resistance on the provider path

■ In response to Fast Role Swap request, turns OFF external consumer N-channel Field Effect Transistor (NFET) and turns ON internal provider load switch

#### LDO

■ Integrated high-voltage LDO operational up to 21.5 V for dead battery mode operation

#### 32-bit MCU Subsystem

- 48-MHz Arm Cortex-M0 CPU

- 64-KB Flash

- 96-KB ROM

- 16-KB SRAM

#### **Integrated Digital Blocks**

- Two integrated timers and counters to meet response times required by the USB-PD protocol

- Four run-time serial communication blocks (SCBs) with reconfigurable I<sup>2</sup>C, SPI, or UART functionality

#### Authentication

■ True Random Number Generator

#### Clocks and Oscillators

■ Integrated oscillator eliminating the need for an external clock

#### **Operating Range**

- VSYS (2.75 V-5.5 V)

- VBUS (4 V-21.5 V)

#### Hot-Swappable I/Os

■ I<sup>2</sup>C pins from SCB0 are hot-swappable

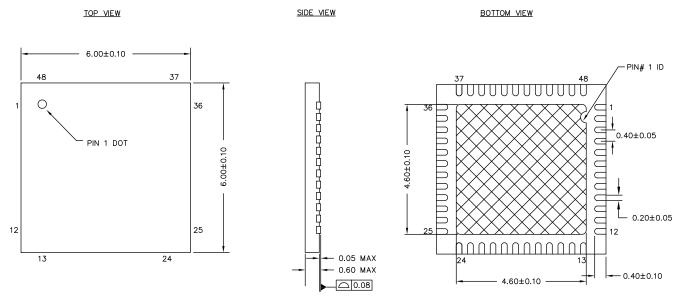

#### **Packages**

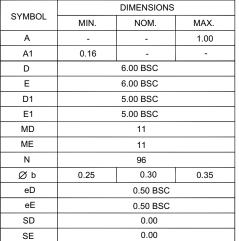

- CCG6DF: 6.0 mm × 6.0 mm × 1.0 mm, 96-ball BGA with 0.5-mm pitch

- CCG6SF: 6.0 mm × 6.0 mm × 0.6 mm, 48-pin QFN with 0.4-mm pitch

#### Notes

- 1. DFP refers to power source.

- 2. UFP refers to power sink.

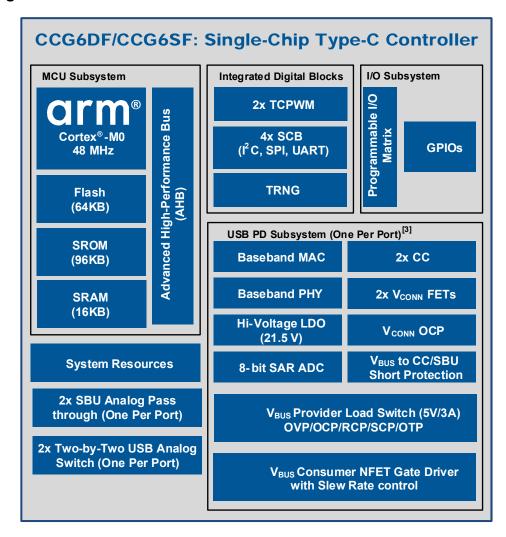

## **Logic Block Diagram**

#### Note

<sup>3.</sup> Only one USB-PD subsystem exists for CCG6SF devices since it has only one Type-C port available.

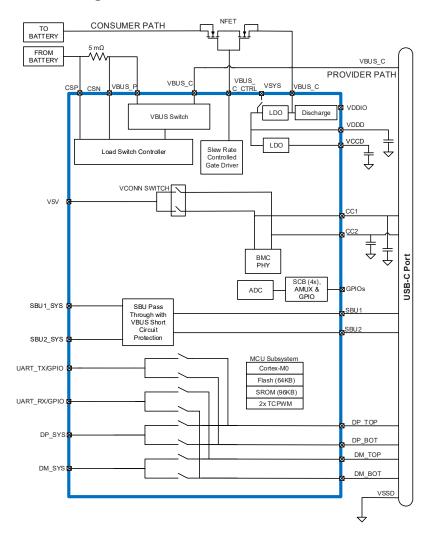

## **CCG6DF/CCG6SF Functional Diagram**

#### Note

To simplify, the functional block diagram is shown only for one port.

## **Contents**

| Functional Overview                              | 5  |

|--------------------------------------------------|----|

| MCU Subsystem                                    | 5  |

| USB-PD Subsystem (SS)                            |    |

| Provider Load Switch                             |    |

| Serial Communication Block (SCB)                 |    |

| Timer, Counter, Pulse-Width Modulator            |    |

| (TCPWM)                                          | 7  |

| True Random Number Generator (TRNG)              |    |

| GPIO Interface                                   | 7  |

| System Resources                                 | 7  |

| Power                                            |    |

| Pinouts                                          |    |

| Application Diagrams                             | 15 |

| CCG6DF Layout Design Guidelines                  |    |

| for BGA Package                                  | 17 |

| Usage of Via Size of 8-mil drill/16-mil Diameter |    |

| and 10-mil drill/16-mil Diameter                 | 17 |

| CCG6SF Layout Design Guidelines                  |    |

| for 48-QFN Package                               | 24 |

| Recommended Pad Size                             | 24 |

| Stackup                                          | 25 |

| 48-QFN Fanout                                    | 25 |

| Via Count on Thermal Pads                        |    |

| Via Count for VBUS_P and VBUS_C Pads             | 26 |

| High-Speed                                      |    |

|-------------------------------------------------|----|

| (DP/DM SYS, DP/DM BOT, DP/DM TOP)               |    |

| USB Connections Fanout                          | 27 |

| CC Connections                                  | 27 |

| VDDIO, VCCD, VSYS, and VDDD Connections         | 28 |

| Electrical Specifications                       |    |

| Absolute Maximum Ratings                        |    |

| Device-Level Specifications                     |    |

| Digital Peripherals                             |    |

| System Resources                                |    |

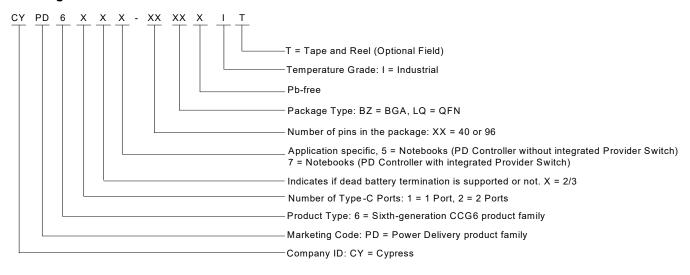

| Ordering Information                            |    |

| Ordering Code Definitions                       |    |

| Packaging                                       |    |

| Acronyms                                        |    |

| Document Conventions                            |    |

| Units of Measure                                |    |

| References and Links to Applications Collateral | 48 |

| Document History Page                           |    |

| Sales, Solutions, and Legal Information         |    |

| Worldwide Sales and Design Support              | 50 |

| Products                                        |    |

| PSoC <sup>®</sup> Solutions                     | 50 |

| Cypress Developer Community                     |    |

| Technical Support                               |    |

|                                                 |    |

#### **Functional Overview**

#### **MCU Subsystem**

#### CPU

The Cortex M0 in CCG6DF and CCG6SF devices is a 32-bit MCU, which is optimized for low-power operation with extensive clock gating. It mostly uses 16-bit instructions and executes a subset of the Thumb-2 instruction set, which enables fully compatible binary upward migration of code to higher performance processors such as Cortex M3 and M4. Also included is a hardware multiplier, which provides a 32-bit result in one cycle. It includes an Interrupt Controller (the NVIC block) with 32 Interrupt inputs and a Wakeup Interrupt Controller (WIC), which can wake the processor up from Deep Sleep mode.

#### Flash, SROM, and RAM

The 64-KB Flash and 96-KB ROM store the firmware implementing PD functionality.

The 16-KB RAM is used under software control to store temporary status of system variables and parameters. A supervisory ROM that contains boot and configuration routines is provided.

#### USB-PD Subsystem (SS)

This subsystem provides the interface to the Type-C USB port. This subsystem comprises of:

- USB-PD Physical Layer

- VCONN FETs

- ADC

- SBU pass-through switch and USB HS mux

- Undervoltage, overvoltage and Reverse-Current Protection on VBUS

- High-side current sense amplifier for VBUS

- VBUS Discharge

- VBUS Regulator

- Consumer Gate Driver for VBUS NFET

- Integrated VBUS Provider path load switch with FRS

- VBUS tolerant SBU and CC pins

#### USB-PD Physical Layer

The USB-PD subsystem contains the USB-PD physical layer block and supporting circuits. The USB-PD Physical Layer consists of a transmitter and receiver that communicate BMC encoded data over the CC channel per the PD 3.0 standard. All communication is half-duplex. The Physical Layer or PHY practices collision avoidance to minimize communication errors on the channel.

In addition, the USB-PD block includes all termination resistors ( $R_P$  and  $R_D$ ) and their switches as required by the USB Type-C spec. Rp and Rd resistors are required to implement connection detection, plug orientation detection and for establishment of the USB source/sink roles. The  $R_P$  resistor is implemented as a current source.

The  $R_D$  resistors on CC pins are required even when the part is not powered on. This is required for dead battery termination detection and charging.

To support the latest USB-PD 3.0 specification, CCG6DF and CCG6SF devices implement the FRS feature. Fast Role Swap enables externally powered docks and hubs to rapidly switch to bus power when their external power supply is removed. This feature is supported for provider N-FET Gate Driver Output (NGDO). SCP and RCP fault detection are not enabled during the FRS sequence and it is assumed that provider side supply is present and higher than 4.85 V.

CCG6DF and CCG6SF devices are designed to be fully interoperable with revision 3.0 of the USB Power Delivery specification as well as revision 2.0 of the USB Power Delivery specification.

#### **VCONN FET**

CCG6DF and CCG6SF devices have power supply input V5V pin for providing power to EMCA cables through integrated VCONN FETs. There are two VCONN FETs per port in CCG6DF and CCG6SF devices to power either CC1 or CC2 pins. These FETs source a minimum of 1.5-W power per port over the valid VCONN range of 4.85 V to 5.5 V on the CC1/2 pins when providing power to EMCA cables. At any given time, only one of the VCONN FETs is in ON state to provide VCONN on either CC1 or CC2 lines depending on the cable orientation. The floating V5V pin does not cause CCG6DF to malfunction and draw more current.

#### ADC

CCG6DF and CCG6SF devices have a low power 8-bit SAR ADC that has access to the chip-wide analog mux. All GPIOs on these devices have access to the ADCs through the chip-wide analog mux.

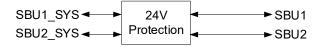

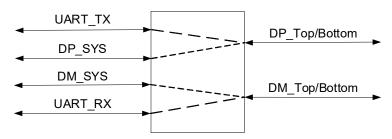

SBU Pass-Through Switch and USB HS Mux

CCG6DF has integrated 2x SBU pass-through switches and 2x high-speed (480 Mbps) switches as shown in Figure 1.

The SBU switch is a simple pass-through switch. The Type-C facing SBU pins are protected from accidental short to VBUS.

The HS mux contains a  $2\times 2$  cross bar switch to route the system DP/DM lines to the Type-C top or bottom lines as per the CC (Type-C plug) orientation and connect the Debug pins to unused DP or DM top or bottom pins.

Figure 1. SBU Protection and High-Speed Crossbar Switch Block Diagram

#### SBU Protection Internal Block Diagram

HS Cross Bar Switch Internal Block Diagram

#### **Provider Load Switch**

CCG6DF and CCG6SF devices have an integrated provider load switch with the following functions.

#### Undervoltage and Overvoltage Protection on VBUS

CCG6DF and CCG6SF devices implement an undervoltage/overvoltage (UVOV) detection circuit for the VBUS supply. The thresholds for both OCP and UVOV are programmable.

#### High-side Current Sense Amplifier for VBUS

CCG6DF and CCG6SF devices support the programmable threshold VBUS current sensing through VBUS provider path. External resistor (5 m $\Omega$ ) placed in VBUS provider path connecting to the chip, the drop across this resistor is monitored to sense the magnitude of current.

#### VBUS Reverse Current Protection

CCG6DF and CCG6SF devices restrict reverse current to zero on the VBUS provider path when the Type-C VBUS is greater than VIN (provider voltage before the VBUS NFET).

#### VBUS Short Circuit Protection

CCG6DF and CCG6SF devices have a VBUS short circuit protection function of which the SCP threshold is programmable. Whenever current through the VBUS Provider Load Switch exceeds the programmed threshold, the SCP gets triggered instantly and turns off the VBUS provider path within a short duration.

### VBUS Discharge

CCG6DF and CCG6SF devices support high-voltage (21.5 V) VBUS discharge circuitry inside. After cable removal detection, the chips discharge the residual charge and bring the floating VBUS to less than 0.8 V.

#### VBUS Regulator

CCG6DF and CCG6SF devices can either be powered by VSYS or VBUS power supplies. There is one VBUS per port. Hence the CCG6DF device can be powered by either VBUS (Port0 or Port1) or VSYS. A regulator operating on these power supplies derives the chip operating supply. When both power supplies are present, VSYS always takes priority over VBUS supplies. In absence of VSYS, the regulator powers the chip from VBUS.

#### Gate Driver for VBUS NFET

CCG6DF and CCG6SF devices have integrated gate drivers to drive external NFETs on the VBUS consumer path. The provider NFETs are integrated. The consumer side supports only the external NFET driver and these NFETs must be capable of supporting ±VBUS\_MAX VGS. CCG6DF and CCG6SF must be in active mode to enable the consumer-side NGDO.

#### VBUS Tolerant SBU and CC Lines

CCG6DF and CCG6SF devices support VBUS tolerant SBU and CC lines. In case of SBU/CC short to VBUS through connectors, these lines are protected internally. Accidental shorts may occur because the SBU/CC pins are placed next to the VBUS pins in the USB Type-C connector. A Power Delivery controller without the high-voltage VBUS short protection will be damaged in the event of such accidental shorts. When overvoltage is detected on the SBU/CC lines, the internal protection circuit will turn off the connection between the Type-C connector and the rest of the device.

#### Serial Communication Block (SCB)

CCG6DF and CCG6SF devices have four SCB blocks that can be configured for  $I^2C$ , SPI, or UART. These blocks implement full multi-master and slave  $I^2C$  interfaces capable of multi-master arbitration.  $I^2C$  is compatible with the standard Philips  $I^2C$  Specification V3.0. These blocks operate at speeds of up to 1 Mbps and have flexible buffering options to reduce interrupt overhead and latency for the CPU.

The SCB blocks support 8-byte deep FIFOs for Receive and Transmit, which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read data on time.

#### Timer, Counter, Pulse-Width Modulator (TCPWM)

The TCPWM block of CCG6DF and CCG6SF supports up to two timers or counters or pulse-width modulators. These timers are available for internal timer use by firmware or for providing PWM-based functions on the GPIOs.

#### True Random Number Generator (TRNG)

In notebook designs, CCG6DF's and CCG6SF's TRNG block is used in authenticating connected devices such as power adapters or docks that include support for USB Type-C Authentication Specification (USBTCAS). CCG6DF and CCG6SF devices, within notebook applications, are implemented as an initiate role as defined in USBTCAS, while the connected device would implement the responder-role. USBTCAS provides a means for authenticating Type-C devices with regards to identification and configuration.

#### **GPIO Interface**

The CCG6DF device has 23 GPIOs and the CCG6SF device has 19 GPIOs including the I<sup>2</sup>C and SWD pins, which can also be used as GPIOs.

The GPIO block implements the following:

- Eight drive strength modes including strong push-pull, resistive pull-up and pull-down, weak (resistive) pull-up and pull-down, open drain and open source, input only, and disabled.

- Input threshold select (CMOS or LVTTL)

- Individual control of input and output disables.

- Hold mode for latching previous state (used for retaining I/O state in Deep Sleep mode).

- Selectable slew rates for dV/dt related noise control.

During power-on and reset, the blocks are forced to the Disable state so as not to crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a high-speed I/O matrix is used to multiplex between various signals that may

connect to an I/O pin. Pin locations for fixed-function peripherals, such as USB Type-C ports, are also fixed to reduce internal multiplexing complexity. Data Output Registers and Pin State Register store, respectively, the values to be driven on the pins and the states of the pins themselves. The configuration of the pins can be done by programming of registers through software for each digital I/O Port.

Every I/O pin can generate an interrupt if so enabled and each I/O port has an IRQ and ISR vector associated with it.

The I/O ports retain their state during Deep Sleep mode or remain ON. If operation is restored using reset, then the pins shall go the High-Z state. If operation is restored by an interrupt event, then the pin drivers shall retain their state until firmware chooses to change it. The I/Os (on data bus) do not draw current on power down.

All GPIOs reside in a separate I/O power domain – VDDIO to provide flexible system-level interfacing.

#### **System Resources**

Watchdog Timer (WDT)

A watchdog timer is implemented in the Clock block running from the internal low-speed oscillator (ILO) for CCG6DF and CCG6SF devices. This allows watchdog operation during Deep Sleep and generates a Watchdog Reset if not serviced before the timeout occurs.

In addition to the chip-level watchdog timer, each USB-PD block implements a counter based on ILO (Low frequency) clock which can be used to wake/trigger the part periodically. This counter can be used to drive any periodic tasks to be performed by the device.

#### Clock System

CCG6DF and CCG6SF have a fully integrated clock with no external crystal required. CCG6DF/CCG6SF clock system is responsible for providing clocks to all subsystems that require clocks (SCB and USB-PD) and for switching between different clock sources, without glitches. The clock system for these devices consists of the internal main oscillator (IMO) and the ILO.

#### IMO Clock Source

The IMO is the primary source of internal clocking in CCG6DF and CCG6SF devices with an accuracy of  $\pm 2\%$ . The default IMO frequency for CCG6DF and CCG6SF devices is 48 MHz  $\pm 2\%$ .

#### ILO Clock Source

The ILO is a very low power, relatively inaccurate, oscillator, which is primarily used to generate clocks for peripheral operation in USB Suspend (Deep Sleep) mode. The typical frequency of the ILO is 32-kHz.

#### **Power**

CCG6DF can operate either from VBUS\_C (from Port 0 and/or 1) or  $V_{SYS}$  supply inputs. In addition, there is V5V supply pin, which sources the  $V_{CONN}$  supply to the Type-C connector, the valid levels on V5V supply can range from 4.85-5.5 V. V5V does not power the chip. The chip's internal operating power supply is derived from  $V_{SYS}$  (2.75 V to 5.5 V) or VBUS (4 V- 21.5 V). In dead battery mode, the chip can be supplied power from Type-C VBUS (from port 0 and/or 1). In UFP, DFP, and DRP modes (when the system battery is charged), the chip is powered via  $V_{SYS}$ . CCG6DF and CCG6SF devices support power modes to minimize energy consumption when not actively involved in data communication over the Type-C port.

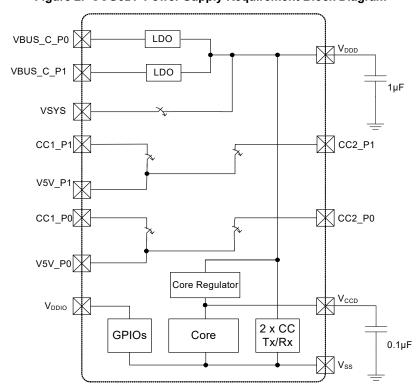

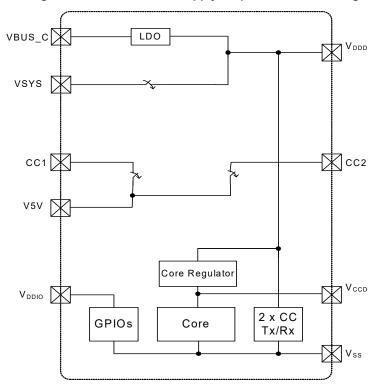

Figure 2 and Figure 3 show an overview of the power system requirement for CCG6DF and CCG6SF devices. CCG6DF and CCG6SF devices have two different power modes: Active and Deep Sleep, transitions between which are managed by the Power System. A separate power domain,  $V_{DDIO}$ , is provided for the GPIOs and  $V_{DDD}$  which generates 3.3 V from internal regulator.  $V_{DDD}$  can be shorted to  $V_{DDIO}$ .  $V_{DDD}$  and  $V_{CCD}$  are not recommended to be used as power supplies for other circuits on the system. Also,  $V_{DDD}$  and  $V_{CCD}$  pins cannot be treated as power sources for the chip.The  $V_{CCD}$  pin, the output of the core (1.8 V) regulator, is brought out for connecting a 0.1- $\mu$ F capacitor for the regulator stability only.

Figure 2. CCG6DF Power Supply Requirement Block Diagram

Figure 3. CCG6SF Power Supply Requirement Block Diagram

Table 1. CCG6DF/CCG6SF Power Modes

| Mode       | Description                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|

| IRACAT     | Power is Valid and XRES is not asserted. An internal reset source is asserted or Sleep Controller is sequencing the system out of reset. |

| ACTIVE     | Power is Valid and CPU is executing instructions. This mode includes the critical Type-C power spec requirement.                         |

| DEEP SLEEP | Main regulator and most hard-IP are shut off. DeepSleep regulator powers logic, but only low-frequency clock is available.               |

## **Pinouts**

Table 2. Pinout for CYPD6227-96BZXI

| Group Name      | Pin Name        | Port   | Pin | Description                                                                          |

|-----------------|-----------------|--------|-----|--------------------------------------------------------------------------------------|

|                 | CC1_P0          | Analog | В3  | USB PD Port-0 connector detect/Configuration Channel 1                               |

| USB Type-C      | CC2_P0          | Analog | B5  | USB PD Port-0 connector detect/Configuration Channel 2                               |

| ОЗВ Туре-С      | CC1_P1          | Analog | K5  | USB PD Port-1 connector detect/Configuration Channel 1                               |

|                 | CC2_P1          | Analog | K3  | USB PD Port-1 connector detect/Configuration Channel 2                               |

|                 | DP_SYS_P0       | Analog | K11 | USB 2.0 DP from the Host System: Port-0                                              |

|                 | DM_SYS_P0       | Analog | J11 | USB 2.0 DM from the Host System: Port-0                                              |

|                 | UART_TX_P0/P1.4 | GPIO   | H10 | UART Tx from Host System: Port-0/GPIO                                                |

|                 | UART_RX_P0/P1.3 | GPIO   | G10 | UART Rx from Host System: Port-0/GPIO                                                |

|                 | DP_BOT_P0       | Analog | K10 | USB 2.0 DP from Bottom of Type-C Connector: Port-0                                   |

|                 | DM_BOT_P0       | Analog | J10 | USB 2.0 DM from Bottom of Type-C Connector: Port-0                                   |

|                 | DM_TOP_P0       | Analog | H11 | USB 2.0 DM from Top of Type-C Connector: Port-0                                      |

|                 | DP_TOP_P0       | Analog | G11 | USB 2.0 DP from Top of Type-C Connector: Port-0                                      |

|                 | SBU2_P0         | Analog | A4  | Type-C Sideband Use signal – Connector side: Port-0                                  |

|                 | SBU1_P0         | Analog | A5  | Type-C Sideband Use signal – Connector side: Port-0                                  |

|                 | SBU1_SYS_P0     | Analog | В6  | Type-C Sideband Use signal – System side: Port-0                                     |

| Muyaa/Cyritahaa | SBU2_SYS_P0     | Analog | A6  | Type-C Sideband Use signal – System side: Port-0                                     |

| Muxes/Switches  | DP_SYS_P1       | Analog | L6  | USB 2.0 DP from the Host System: Port-1                                              |

|                 | DM_SYS_P1       | Analog | L5  | USB 2.0 DM from the Host System: Port-1                                              |

|                 | UART_TX_P1/P0.0 | GPIO   | L4  | UART Tx from Host System: Port-1/GPIO                                                |

|                 | UART_RX_P1/P0.1 | GPIO   | K6  | UART Rx from Host System: Port-1/GPIO                                                |

|                 | DP_BOT_P1       | Analog | K8  | USB 2.0 DP from Bottom of Type-C Connector: Port-1                                   |

|                 | DM_BOT_P1       | Analog | K7  | USB 2.0 DM from Bottom of Type-C Connector Port-1                                    |

|                 | DM_TOP_P1       | Analog | L7  | USB 2.0 DM from Top of Type-C Connector: Port-1                                      |

|                 | DP_TOP_P1       | Analog | L8  | USB 2.0 DP from Top of Type-C Connector: Port-1                                      |

|                 | SBU2_P1         | Analog | A9  | Type-C Sideband Use signal – Connector side: Port-1                                  |

|                 | SBU1_P1         | Analog | A8  | Type-C Sideband Use signal – Connector side Port-1                                   |

|                 | SBU1_SYS_P1     | Analog | B7  | Type-C Sideband Use signal – System side: Port-1                                     |

|                 | SBU2_SYS_P1     | Analog | A7  | Type-C Sideband Use signal – System side: Port-1                                     |

| VBUS Control    | VBUS_C_CTRL_P0  | Analog | А3  | Full rail control I/O for enabling/disabling Consumer load NFET of USB Type-C Port-0 |

| VBOS CONTO      | VBUS_C_CTRL_P1  | Analog | L3  | Full rail control I/O for enabling/disabling Consumer load NFET of USB Type-C Port-1 |

|                 | CSP_P0          | Analog | A11 | Current Sense Positive Input for VBUS side external Rsense: Port-0                   |

| VBUS OCP        | CSN_P0          | Analog | A10 | Current Sense Negative input for other side of external Rsense: Port-0               |

| 1200 001        | CSP_P1          | Analog | L11 | Current Sense Positive Input for VBUS side external Rsense: Port-1                   |

|                 | CSN_P1          | Analog | L10 | Current Sense Negative input for other side of external Rsense: Port-1               |

Table 2. Pinout for CYPD6227-96BZXI (continued)

| Group Name                  | Pin Name            | Port   | Pin                                          | Description                                                                                        |

|-----------------------------|---------------------|--------|----------------------------------------------|----------------------------------------------------------------------------------------------------|

|                             | I2C_SDA_SCB1/P0.2   | GPIO   | K9                                           | SCB1 data for communicating with SoC or TBT controller/GPIO                                        |

|                             | I2C_SCL_SCB1/P0.3   | GPIO   | H7                                           | SCB1 clock for communicating with SoC or TBT controller / GPIO                                     |

|                             | I2C_INT_EC/P1.2     | GPIO   | F11                                          | Embedded Controller interrupt / GPIO                                                               |

|                             | P2.4                | GPIO   | D10                                          | GPIO                                                                                               |

|                             | I2C_INT_TBT_P0/P0.4 | GPIO   | L9                                           | ThunderBolt interrupt for Port-0 / GPIO                                                            |

|                             | SWD_IO/P1.1         | GPIO   | G8                                           | Serial Wire Debug I/O / GPIO                                                                       |

|                             | SWD_CLK/P1.0        | GPIO   | F10                                          | Serial Wire Debug Clock / GPIO                                                                     |

|                             | HPD_P0/P2.0         | GPIO   | F8                                           | Hot Plug Detect I/O for Port-0 / GPIO                                                              |

|                             | I2C_SDA_SCB2/P2.1   | GPIO   | E11                                          | SCB2 data for configuring Re-timer or DP/USB<br>Multi-Function MUX/ GPIO                           |

| GPIOs and Serial Interfaces | I2C_SCL_SCB2/P2.2   | GPIO   | E10                                          | SCB2 clock for configuring Re-timer or DP/USB<br>Multi-Function MUX/ GPIO                          |

|                             | P2.3                | GPIO   | E8                                           | GPIO                                                                                               |

|                             | I2C_INT_TBT_P1/P0.5 | GPIO   | H8                                           | ThunderBolt interrupt for Port-1 / GPIO                                                            |

|                             | P2.5                | GPIO   | D8                                           | GPIO                                                                                               |

|                             | I2C_SCL_SCB0/P4.0   | GPIO   | D11                                          | SCB0 clock for communicating with Embedded controller / GPIO                                       |

|                             | I2C_SDA_SCB0/P4.1   | GPIO   | C11                                          | SCB0 data for communicating with Embedded controller / GPIO                                        |

|                             | P3.0                | GPIO   | B10                                          | GPIO                                                                                               |

|                             | I2C_SDA_SCB3/P3.1   | GPIO   | B11                                          | SCB3 data / GPIO                                                                                   |

|                             | I2C_SCL_SCB3/P3.2   | GPIO   | В9                                           | SCB3 clock / GPIO                                                                                  |

|                             | HPD_P1/P3.3         | GPIO   | B8                                           | Hot Plug Detect I/O for Port-1 / GPIO                                                              |

| Reset                       | XRES                | Analog | C10                                          | Reset input                                                                                        |

|                             | VBUS_C_P0           | Power  | A1,A2,B1,B2,C1                               | Type-C VBUS Connector Input for Port-0 (4-V to 21.5-V)                                             |

|                             | VBUS_C_P1           | Power  | J1,K1,K2,L1,L2                               | Type-C VBUS Connector Input for Port-1 (4-V to 21.5-V)                                             |

|                             | VBUS_P_P0           | Power  | C2,D1,D2,E1,E2                               | VBUS Provider Input for Port-0 (4-V to 5.5-V)                                                      |

|                             | VBUS_P_P1           | Power  | G1,G2,H1,H2,J2                               | VBUS Provider Input for Port-1 (4-V to 5.5-V)                                                      |

|                             | VSYS                | Power  | F4                                           | 2.75-V to 5.5-V supply for the system                                                              |

| Power                       | VDDD                | Power  | G7                                           | VDDD supply output 1. VSYS powered - (Min: VSYS-50 mV) 2.7 to 5.5 2. VBUS powered - 3.0 V to 3.6 V |

|                             | VDDIO               | Power  | F7                                           | At system-level short the VDDD to VDDIO                                                            |

|                             | VCCD                | Power  | E7                                           | 1.8-V regulator output for filter capacitor. This pin cannot drive external load.                  |

|                             | V5V_P0              | Power  | B4                                           | 4.85-V to 5.5-V supply for VCONN FET of Type-C:<br>Port-0                                          |

|                             | V5V_P1              | Power  | K4                                           | 4.85-V to 5.5-V supply for VCONN FET of Type-C:<br>Port-1                                          |

| Ground                      | VSSD                | Ground | D7, E5, E6, F1,<br>F2, F5, F6, G4,<br>G5, G6 | Ground                                                                                             |

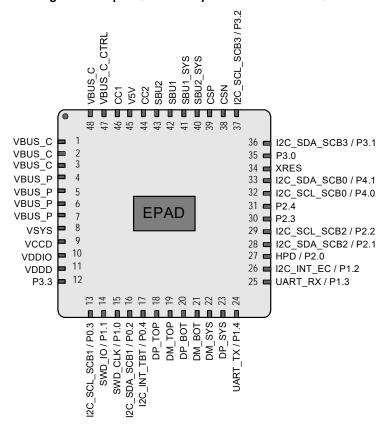

Figure 4. 96-Ball BGA Pin Map (Top View) for CYPD6227-96BZXI

|   | 1             | 2         | 3                  | 4                    | 5             | 6                    | 7                     | 8                       | 9                       | 10                    | 11                    |

|---|---------------|-----------|--------------------|----------------------|---------------|----------------------|-----------------------|-------------------------|-------------------------|-----------------------|-----------------------|

| Α | VBUS_C_<br>P0 | VBUS_C_P0 | VBUS_C_<br>CTRL_P0 | SBU2_P0              | SBU1_P0       | SBU2_SYS-<br>_P0     | SBU2_SYS-<br>_P1      | SBU1_P1                 | SBU2_P1                 | CSN_P0                | CSP_P0                |

| В | VBUS_C_<br>P0 | VBUS_C_P0 | CC1_P0             | V5V_P0               | CC2_P0        | SBU1_SYS-<br>_P0     | SBU1_SYS-<br>_P1      | HPD_P1/<br>P3.3         | I2C_SCL_<br>SCB3/P3.2   | P3.0                  | I2C_SDA_<br>SCB3/P3.1 |

| С | VBUS_C_<br>P0 | VBUS_P_P0 |                    |                      |               |                      |                       |                         |                         | XRES                  | I2C_SDA<br>SCB0/P4.1  |

| D | VBUS_P_P0     | VBUS_P_P0 |                    |                      | DNU           | DNU                  | VSSD                  | P2.5                    |                         | P2.4                  | I2C_SCL_<br>SCB0/P4.0 |

| E | VBUS_P_P0     | VBUS_P_P0 |                    | DNU                  | VSSD          | VSSD                 | VCCD                  | P2.3                    |                         | I2C_SCL_<br>SCB2/P2.2 | I2C_SDA_<br>SCB2/P2.1 |

| F | VSSD          | VSSD      |                    | VSYS                 | VSSD          | VSSD                 | VDDIO                 | HPD_P0/<br>P2.0         |                         | SWD_CLK/<br>P1.0      | I2C_INT_EC/<br>P1.2   |

| G | VBUS_P_P1     | VBUS_P_P1 |                    | VSSD                 | VSSD          | VSSD                 | VDDD                  | SWD_IO/<br>P1.1         |                         | UART_RX_<br>P0/P1.3   | DP_TOP_P0             |

| н | VBUS_P_P1     | VBUS_P_P1 |                    | DNU                  | DNU           | DNU                  | I2C_SCL_<br>SCB1/P0.3 | I2C_INT_TBT<br>_P1/P0.5 |                         | UART_TX_<br>P0/P1.4   | DM_TOP_P0             |

| J | VBUS_C_<br>P1 | VBUS_P_P1 |                    |                      |               |                      |                       |                         |                         | DM_BOT_<br>P0         | DM_SYS_P0             |

| K | VBUS_C_<br>P1 | VBUS_C_P1 | CC2_P1             | V5V_P1               | CC1_P1        | UART_RX-<br>_P1/P0.1 | DM_BOT_<br>P1         | DP_BOT_<br>P1           | I2C_SDA_<br>SCB1/P0.2   | DP_BOT_P0             | DP_SYS_P0             |

| L | VBUS_C_<br>P1 | VBUS_C_P1 | VBUS_C_<br>CTRL_P1 | UART_TX-<br>_P1/P0.0 | DM_SYS_<br>P1 | DP_SYS_<br>P1        | DM_TOP_<br>P1         | DP_TOP_P1               | I2C_INT_TBT<br>_P0/P0.4 | CSN_P1                | CSP_P1                |

Table 3. Pinout for CYPD6127-48LQXI

| <b>Group Name</b>              | Pin Name          | Port   | Pin | Description                                                                   |

|--------------------------------|-------------------|--------|-----|-------------------------------------------------------------------------------|

| HOD To the O                   | CC1               | Analog | 46  | USB PD connector detect/Configuration Channel 1                               |

| USB Type-C                     | CC2               | Analog | 44  | USB PD connector detect/Configuration Channel 2                               |

|                                | DP_SYS            | Analog | 23  | USB 2.0 DP from the Host System                                               |

|                                | DM_SYS            | Analog | 22  | USB 2.0 DM from the Host System                                               |

|                                | UART_TX/P1.4      | GPIO   | 24  | UART Tx from Host System/GPIO                                                 |

|                                | UART_RX/P1.3      | GPIO   | 25  | UART Rx from Host System/GPIO                                                 |

|                                | DP_BOT            | Analog | 20  | USB 2.0 DP from Bottom of Type-C Connector                                    |

| Mux                            | DM_BOT            | Analog | 21  | USB 2.0 DM from Bottom of Type-C Connector                                    |

| IVIUX                          | DM_TOP            | Analog | 19  | USB 2.0 DM from Top of Type-C Connector                                       |

|                                | DP_TOP            | Analog | 18  | USB 2.0 DP from Top of Type-C Connector                                       |

|                                | SBU2              | Analog | 43  | Type-C Sideband Use signal – Connector side                                   |

|                                | SBU1              | Analog | 42  | Type-C Sideband Use signal – Connector side                                   |

|                                | SBU1_SYS          | Analog | 41  | Type-C Sideband Use signal – System side                                      |

|                                | SBU2_SYS          | Analog | 40  | Type-C Sideband Use signal – System side                                      |

| VBUS Control                   | VBUS_C_CTRL       | Analog | 47  | Full rail control I/O for enabling/disabling Consumer load NFET of USB Type-C |

| VBUS OCP                       | CSP               | Analog | 39  | Current Sense Positive Input for VBUS side external Rsense                    |

| VB03 001                       | CSN               | Analog | 38  | Current Sense Negative input for other side of external Rsense                |

|                                | I2C_SDA_SCB1/P0.2 | GPIO   | 16  | SCB1 data / GPIO                                                              |

|                                | I2C_SCL_SCB1/P0.3 | GPIO   | 13  | SCB1 clock / GPIO                                                             |

|                                | I2C_INT_TBT/P0.4  | GPIO   | 17  | ThunderBolt interrupt / GPIO                                                  |

|                                | I2C_INT_EC/P1.2   | GPIO   | 26  | Embedded Controller interrupt / GPIO                                          |

|                                | SWD_IO/P1.1       | GPIO   | 14  | Serial Wire Debug I/O / GPIO                                                  |

|                                | SWD_CLK/P1.0      | GPIO   | 15  | Serial Wire Debug Clock / GPIO                                                |

|                                | HPD/P2.0          | GPIO   | 27  | Hot Plug Detect I/O / GPIO                                                    |

| ODIO I                         | I2C_SDA_SCB2/P2.1 | GPIO   | 28  | SCB2 data / GPIO                                                              |

| GPIOs and<br>Serial Interfaces | I2C_SCL_SCB2/P2.2 | GPIO   | 29  | SCB2 clock / GPIO                                                             |

|                                | P2.3              | GPIO   | 30  | GPIO                                                                          |

|                                | P2.4              | GPIO   | 31  | GPIO                                                                          |

|                                | I2C_SCL_SCB0/P4.0 | GPIO   | 32  | SCB0 clock / GPIO                                                             |

|                                | I2C_SDA_SCB0/P4.1 | GPIO   | 33  | SCB0 data / GPIO                                                              |

|                                | P3.0              | GPIO   | 35  | GPIO                                                                          |

|                                | I2C_SDA_SCB3/P3.1 | GPIO   | 36  | GPIO                                                                          |

|                                | I2C_SCL_SCB3/P3.2 | GPIO   | 37  | GPIO                                                                          |

|                                | P3.3              | GPIO   | 12  | GPIO                                                                          |

| Reset                          | XRES              | Analog | 34  | Reset input                                                                   |

Table 3. Pinout for CYPD6127-48LQXI (continued)

| Group Name | Pin Name | Port   | Pin      | Description                                                                                        |

|------------|----------|--------|----------|----------------------------------------------------------------------------------------------------|

|            | VBUS_C   | Power  | 1,2,3,48 | Type-C VBUS Connector Input (4-V to 21.5-V)                                                        |

|            | VBUS_P   | Power  | 4,5,6,7  | VBUS Provider Input (4-V to 5.5-V)                                                                 |

|            | VSYS     | Power  | 8        | 2.75-V to 5.5-V Supply for the System                                                              |

| Power      | VDDD     | Power  | 11       | VDDD supply output 1. VSYS powered - (Min: VSYS-50 mV) 2.7 to 5.5 2. VBUS powered - 3.0 V to 3.6 V |

|            | VDDIO    | Power  | 10       | At system-level short the VDDD to VDDIO                                                            |

|            | VCCD     | Power  | 9        | 1.8-V regulator output for filter capacitor. This pin cannot drive external load.                  |

|            | V5V      | Power  | 45       | 4.85-V to 5.5-V supply for VCONN FET of Type-C                                                     |

| Ground     | -        | Ground | EPAD     | Ground                                                                                             |

Figure 5. 48-pin QFN Pin Map for CYPD6127-48LQXI

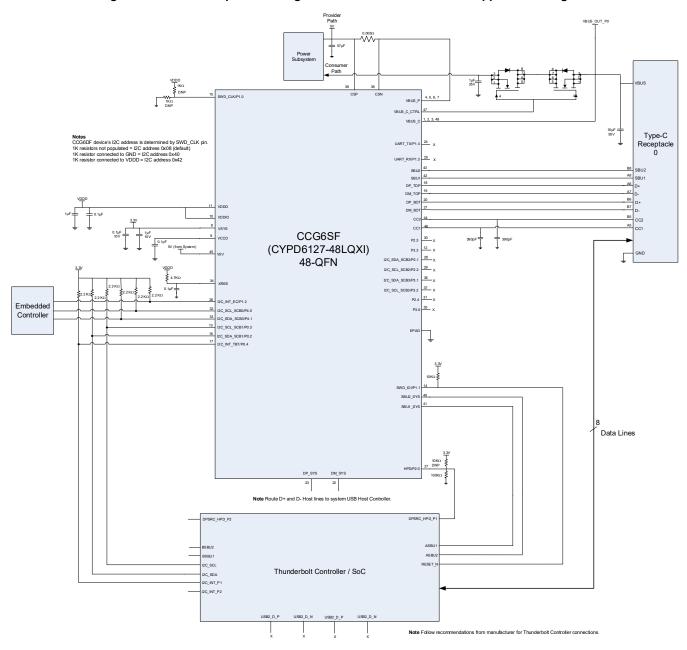

## **Application Diagrams**

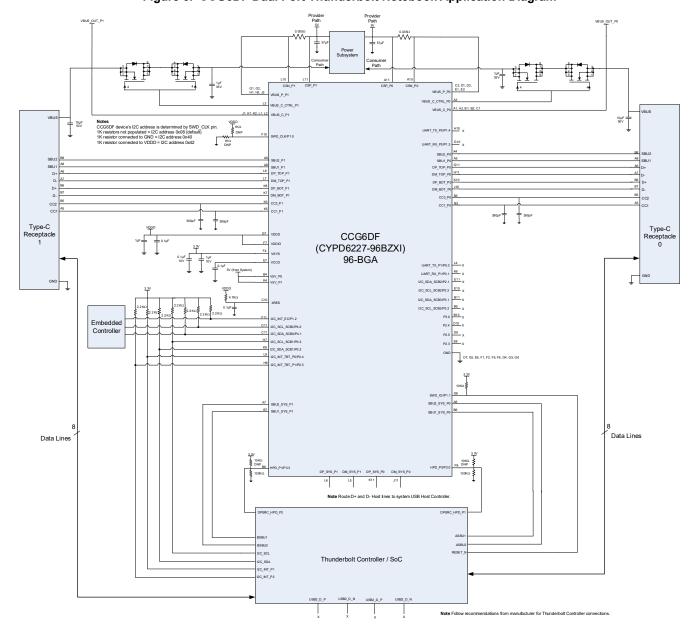

The CCG6DF device communicates with the embedded controller (EC), which manages the Battery Charger Controller (BCC) to control the charging and discharging of the internal battery. It also updates the Thunderbolt Controller via I<sup>2</sup>C to route the HighSpeed signals coming from the Type-C port to the USB host (during normal mode) or the Graphics processor unit (during Display port Alternate mode) or the Thunderbolt Host (during Thunderbolt Alternate mode) based on the alternate mode negotiation.

The CCG6DF device controls the transfer of USB 2.0 DP and DM lines from the top and bottom of the Type-C receptacle to the DP and DM lines of the USB Host controller. CCG6DF offers VBUS Short protection on SBU and CC lines.

The CCG6DF device has integrated VCONN FETs for applications that need to provide power for accessories and cables using the VCONN pin of the Type-C receptacle. The 5-m $\Omega$  resistor between the 5-V supply and the integrated provider FETs is used for overcurrent detection on the VBUS.

Figure 6 illustrates a Dual Port Thunderbolt Notebook DRP application diagram using CYPD6227-96BZXI.

Figure 6. CCG6DF Dual Port Thunderbolt Notebook Application Diagram

Figure 7 illustrates a Single-Port Thunderbolt Notebook DRP application diagram using CYPD6127-48LQXI.

Figure 7. CCG6SF 48-pin QFN Single Port Thunderbolt Notebook Application Diagram

Page 17 of 50

## CCG6DF Layout Design Guidelines for BGA Package

Proper routing and placement help to maintain signal integrity for high-speed signals, improve thermal dissipation and reduce power consumption for CCG6DF/SF. The combination of power and high-speed data signals can be better routed if these design guidelines are followed. It is highly recommended to consult with a PCB manufacturer to verify the manufacturing capabilities to propose the right design guidelines. This section provides layout recommendations which are applicable to both CCG6DF and CCG6SF devices.

Figure 8 shows the CCG6DF 96-BGA device footprint that is recommended. The footprint has oval-shaped pads in specific locations. It is recommended to use oval pads in order to reduce the manufacturing cost by eliminating a High Density Interconnector (HDI) board processing. This method allows the PCB designer to route the inner perimeter balls through the top layer. The balls around the perimeter have their pads in an oval shape with the exception of the corner balls. This footprint is recommended for MDI (Medium Density) PCB designs that are generally less expensive to build.

Figure 8. Top View Standard Footprint (Recommended) for CCG6DF, CCG6SF 96-BGA

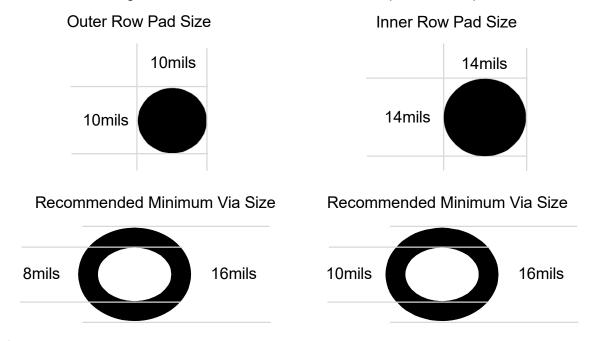

#### Usage of Via Size of 8-mil drill/16-mil Diameter and 10-mil drill/16-mil Diameter

In order to use larger via size of 8/16 (8-mil drill and 16-mil diameter) or 10/16 (10-mil drill and 16-mil diameter), one GPIO (BGA pad D8) is unusable and should be left unconnected. This would free up space underneath the package. This is a critical factor that helps to decide the minimum drill size for the vias. Two different pad sizes for the BGA balls are recommended for better yield in terms of assembly. Note that if GPIO pad D8 cannot be freed up, 6 mil hole / 12 mil diameter via sizes can be used to do PCB trace routing.

Via size of greater than 10-mil drill and 16-mil diameter is not feasible for inner BGA pads. Drill hole size of greater than 10-mils overlaps with the BGA pads and may result in "cold solder" during SMT reflow. Figure 9 shows the recommended 8/16 and 10/16 minimum via sizes (8-mil drill and 16-mil diameter).

Figure 9. Recommended Pad Size and Via Size (8/16 and 10/16)

Layer Stack-up

A typical 8-layer stack up with 1 oz of copper is shown in Figure 10.

Figure 10. Eight Layer Stack-Up

#### Top Layer Fanout

Figure 11 shows a method of routing inner BGA balls and fan-out method for the routing for 8/16 or 10/16 via sizes.

Figure 11. Top Layer Fanout (8/16 or 10/16 via sizes)

#### Via Count for GND Pads

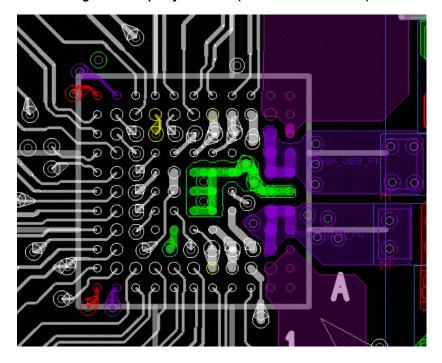

Each via has a thermal resistance of 219 °C/W. Adding three such vias will help reducing thermal resistance to 73 °C/W and would help to distribute the heat better. As shown in Figure 12, it is recommended to short the 6 GND pads with a small split plane on the top layer and have a minimum of two vias to meet the thermal performance. Elevated temperature of more than 100 °C on BGA top may be observed if the via count is lesser than recommended. It is also recommended to have one via on GND pad (D7) with a trace width of 7 mils.

Figure 12. Via Count for GND Pads (8/16 or 10/16 via sizes)

## Via Count for Provider Pads

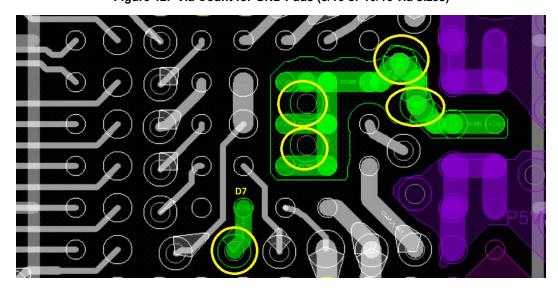

As shown in Figure 13, it is recommended to create a copper pour around the 5 provider pads on the top and bottom layers with minimum of 7 vias. It is also recommended to split the power plane on other layer to meet the thermal performance. These vias play a crucial role in dissipating the heat better.

Figure 13. Via Count for Provider Pads (8/16 or 10/16 via sizes)

High-Speed (DP\_SYS, DM\_SYS) USB Connections

The traces of DP and DM lines with via size of 8-mil drill, 16-mil diameter and 10-mil drill, 16-mil diameter are shown in Figure 14.

Figure 14. DP/DM Traces (8/16 or 10/16 via sizes)

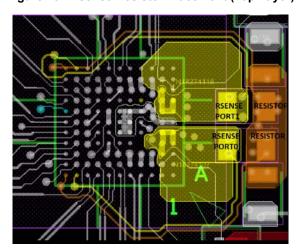

Rsense and Capacitor Connections for Provider VBUS

It is always advisable to keep the sense resistor (Rsense) close to CCG6DF/CCG6SF as it has internal VBUS provider switch. Connection from the regulator to Rsense should be done using big copper shape (pour) for carrying high currents.

The longer the trace length between components, the higher the voltage drop between components. The additional resistance reduces efficiency of the system. The resistance of trace can be calculated from below equation.

$$Rtrace = \rho \times \frac{Tracelength}{Tracewidth \times Tracethickness}$$

Where the bulk resistance  $\rho$ , of copper is 0.67  $\mu\Omega$ /in or 1.7  $\mu\Omega$ /cm at 25 °C.

The differential signal from Rsense should be length matched. The capacitor for Provider VBUS should be as close as possible to the Rsense and connected using copper shape. Figure 15 and Figure 16 show routing for Rsense.

Figure 15. Rsense Resistor Placement (Top Layer)

Figure 16. Rsense Resistor Trace Routing with Kelvin Connection (Inner Layer)

Trace Width Details for Critical Signals

Table 4 provides information on routing trace width for this layout example.

Table 4. Route Trace Width

| Route             | Route Width (mils)<br>(1-oz Copper Thickness) | Remarks / Key Feature / Constraints |

|-------------------|-----------------------------------------------|-------------------------------------|

| CC1, CC2          | 8                                             | Current rating = 500 mA             |

| GPIOs             | 5                                             | -                                   |

| DP/DM/Dsys        | 6 mils width/ 8mils spacing                   | 90-Ω impedance signals              |

| V <sub>DDIO</sub> |                                               | Current rating = 15 mA              |

| $V_{DDD}$         |                                               |                                     |

| V <sub>CCD</sub>  | 10                                            | Current rating = 20 mA              |

| V <sub>SYS</sub>  |                                               |                                     |

| V5V               |                                               | Current rating = 500 mA             |

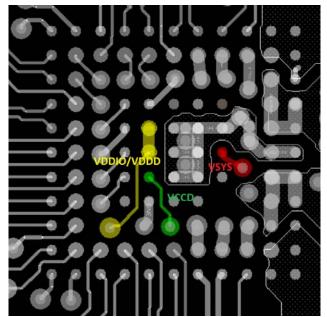

$V_{DDIO}$ ,  $V_{CCD}$ ,  $V_{SYS}$ , and  $V_{DDD}$  Connections

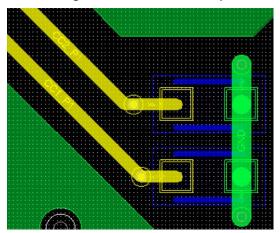

Figure 17 and Figure 18 show how the  $V_{DDIO}$ ,  $V_{DDD}$ ,  $V_{SYS}$ , and  $V_{CCD}$  signals get routed amongst the top and bottom layers.

Figure 17. Top Layer Connection for  $\rm V_{DDIO}, \rm V_{DDD}, \rm V_{SYS}$  and  $\rm V_{CCD}$

Figure 18. Bottom Layer Connection for  $V_{DDIO}$ ,  $V_{DDD}$ ,  $V_{SYS}$  and  $V_{CCD}$

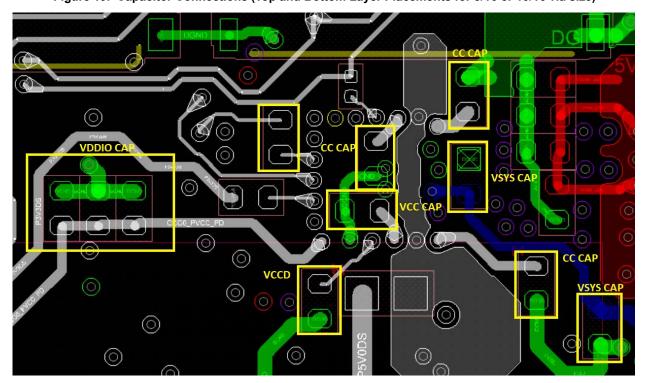

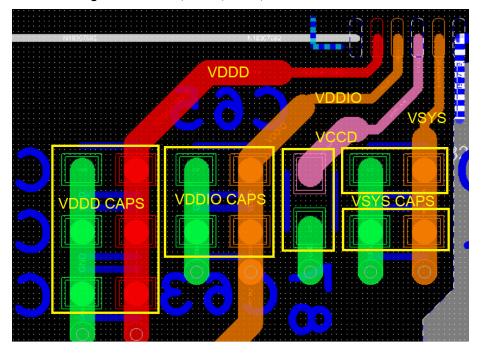

Capacitor Connections for CC Lines and Bypass Capacitors for  $V_{DDIO}$ ,  $V_{DDD}$ ,  $V_{CCD}$ , and  $V_{SYS}$  Pins

Figure 19 shows how the relevant capacitors can be placed for via sizes of 8-mil drill, 16-mil diameter or 10-mil drill, 16-mil diameter.

Figure 19. Capacitor Connections (Top and Bottom Layer Placements for 8/16 or 10/16 via size)

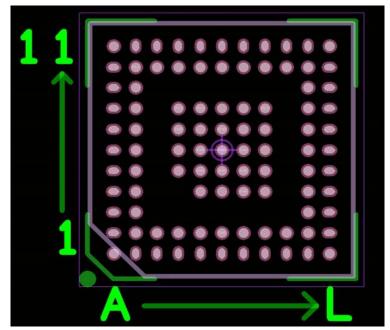

## **CCG6SF Layout Design Guidelines for 48-QFN Package**

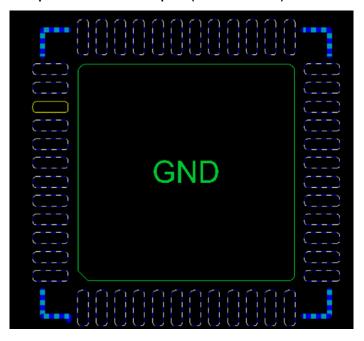

Figure 20 shows the CCG6SF 48-QFN device footprint that is recommended. The footprint has rectangular shaped pads in all pins of this package. It is recommended to use rectangular pads to reduce the manufacturing cost by eliminating a HDI board processing.

Figure 20. Top View Standard Footprint (Recommended) for CCG6SF 48-QFN

## **Recommended Pad Size**

Figure 21 is the recommended pad size for the QFN package.

Figure 21. QFN Pad Size

8 mils

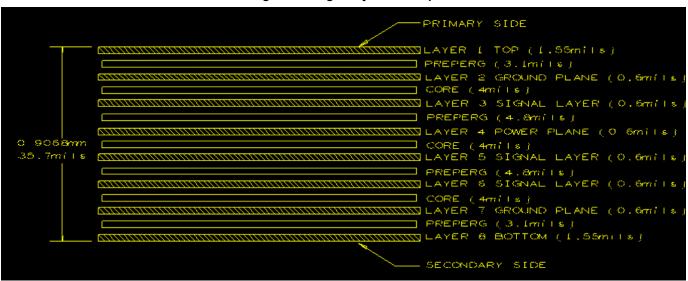

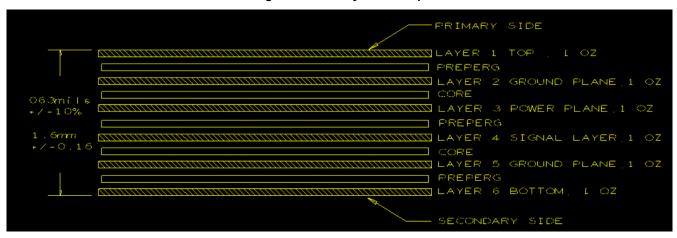

#### Stackup

Figure 22 shows a typical 6-layer stack up with 1 oz of copper.

Figure 22. Six Layer Stack-up

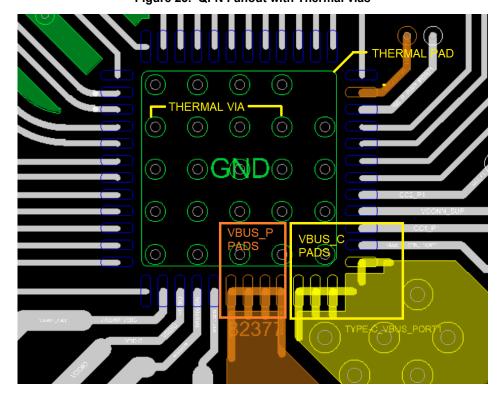

#### 48-QFN Fanout

CCG6SF 48-QFN device uses 5 mil trace width for all the QFN pads and complies to MDI standards. It is better to use 5 mil trace on each of VBUS provider input (VBUS\_P) pads and Type-C VBUS connector input (VBUS\_C) pads and then connect with corresponding power shape. Otherwise, wider trace width would have Non-solder mask between the pads and results in alignment issue during assembly.

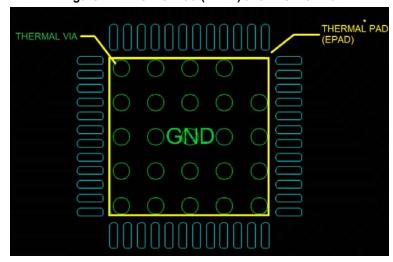

Figure 23. QFN Fanout with Thermal vias

#### Via Count on Thermal Pads

As shown in Figure 24, CCG6SF 48-QFN device has  $5 \times 5$  via array (25 vias) on the thermal pads. It is recommended to have minimum of  $4 \times 4$  via array (16 vias) on the thermal pads to meet the thermal performance. Via array means number of vias present on row and column of the EPAD. Each Via size should be minimum of 10mil drill and 20mil diameter. Each via has a thermal resistance of 179 °C/W. Adding  $4 \times 4$  vias will help reducing thermal resistance to (179/16 vias) 11 °C/W and would help to distribute the heat better. Lesser the thermal resistance better the thermal performance. Power plane is required on this path to able to carry ~6A of current.

Figure 24. Thermal Pad (EPAD) and Thermal Via

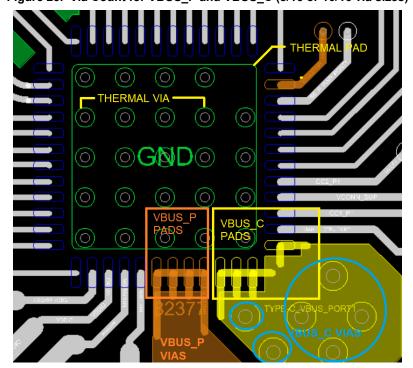

## Via Count for VBUS\_P and VBUS\_C Pads

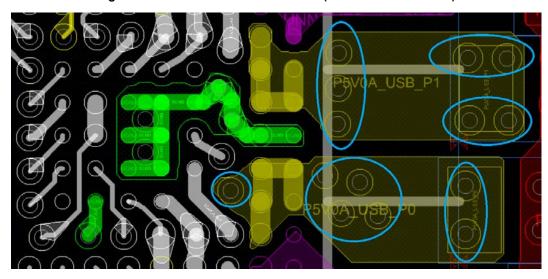

As shown in Figure 25, it is recommended to create a copper pour around the VBUS\_P and VBUS\_C pads on the top and bottom layers with minimum of 6 vias. It is also recommended to split the power plane on other layer to meet the thermal performance. These vias play a crucial role in dissipating the heat better.

Figure 25. Via Count for VBUS P and VBUS C (8/16 or 10/16 via sizes)

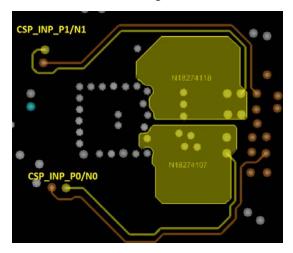

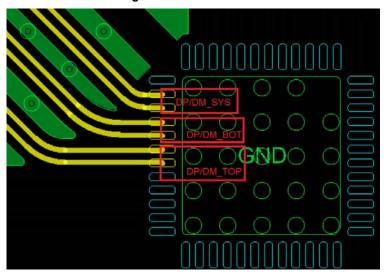

## High-Speed (DP/DM\_SYS, DP/DM\_BOT, DP/DM\_TOP) USB Connections Fanout

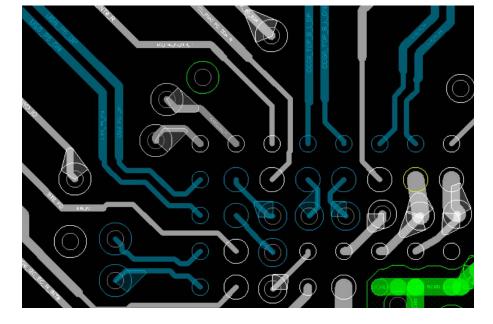

Figure 26 shows differential fanout. The DP/DM lines from CCG6SF to connector should be differentially routed and length match  $\pm 10\%$  tolerance. It should maintain  $90-\Omega$  impedance.

Figure 26. Differential Fanout

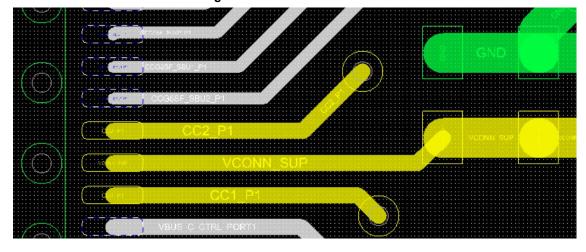

#### **CC Connections**

CC lines for CCG6DF/CCG6SF devices carry ~500-mA current. It is recommended to have 0.15 mm trace width for CC1, CC2 and V5V pads. The capacitors are placed on bottom layer and are routed to the Type-C Connector. The CC1 and CC2 fanout is shown in Figure 27 and Figure 28.

Figure 27. CC1 and CC2 Fanout

Figure 28. CC1 and CC2 Caps

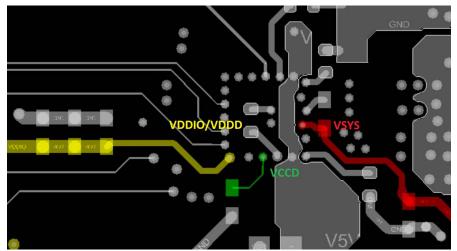

## $\mathbf{V}_{\mathrm{DDIO}},\,\mathbf{V}_{\mathrm{CCD}},\,\mathbf{V}_{\mathrm{SYS}},\,\mathrm{and}\,\,\mathbf{V}_{\mathrm{DDD}}$ Connections

Figure 29 shows how the  $V_{DDIO}$ ,  $V_{DDD}$ ,  $V_{SYS}$ , and  $V_{CCD}$  signals get routed amongst the top and bottom layers.

Figure 29. VDDIO, VCCD, VSYS, and VDDD Connections

## **Electrical Specifications**

## **Absolute Maximum Ratings**

Table 5. Absolute Maximum Ratings<sup>[4]</sup>

| Parameter                   | Description                                                                        | Min                 | Тур | Max                     | Unit | Details/Conditions                                                                                     |

|-----------------------------|------------------------------------------------------------------------------------|---------------------|-----|-------------------------|------|--------------------------------------------------------------------------------------------------------|

| V <sub>SYS_MAX</sub>        | Supply relative to V <sub>SS</sub>                                                 | _                   | -   | 6                       |      |                                                                                                        |

| V <sub>5V_MAX</sub>         | Max supply voltage relative to V <sub>SS</sub>                                     | _                   | -   | 6                       |      |                                                                                                        |

| V <sub>BUS_C</sub>          | V <sub>BUS</sub> voltage relative to Vss                                           | -0.3 <sup>[5]</sup> | -   | 24                      | .,   |                                                                                                        |

| V <sub>DDIO_MAX</sub>       | Max supply voltage relative to V <sub>SS</sub>                                     | -                   | _   | $V_{DDD}$               | V    | _                                                                                                      |

| V <sub>GPIO_ABS</sub>       | Inputs to GPIO, DP/DM mux (UART, SYS, DP/DM_top/bot pins), SBU mux (SBU1/2 pins)   | -0.5                | -   | V <sub>DDIO</sub> + 0.5 |      |                                                                                                        |

| I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                           | -25                 | -   | 25                      |      | _                                                                                                      |

| I <sub>GPIO_INJECTION</sub> | GPIO injection current, Max for $V_{IH} > V_{DDD}$ , and Min for $V_{IL} < V_{SS}$ | -0.5                | ı   | 0.5                     | mA   | Absolute max, current injected per pin                                                                 |

| ESD_HBM                     | Electrostatic discharge human body model                                           | 2200                | -   | -                       |      | Applicable for all pins except SBU1_P0/1, SBU2_P0/1, CC1_0/1, CC2_0/1, VBUS_P_P0/1 & VBUS_C_P0/1 pins. |

| ESD_HBM_SBU                 | Electrostatic discharge human body model for SBU1, SBU2 pins                       | 1100                | -   | -                       | V    | Only applicable to SBU1_P0/1, SBU2_P0/1 pins                                                           |

| ESD_HBM_CC                  | Electrostatic discharge human body model for CC1 and CC2 pins for both ports       | 1100                | -   | -                       |      | Only applicable to CC1_P0/1,<br>CC2_P0/1 pins                                                          |

| ESD_CDM                     | Electrostatic discharge charged device model                                       | 500                 | -   | _                       |      | Charged Device Model ESD                                                                               |

| ESD_HBM_VBUS                | Electrostatic discharge human body<br>model for VBUS_P_P0/1 &<br>VBUS_C_P0/1 pins  | 500                 | _   | _                       | V    | Only applicable to<br>VBUS_P_P0/1 and<br>VBUS_C_P0/1 pins                                              |

| LU                          | Pin current for latch-up                                                           | -100                | _   | 100                     | mA   | _                                                                                                      |

| VCC_PIN_ABS                 | Max voltage on CC1 and CC2 pins                                                    | _                   | _   | 24                      |      |                                                                                                        |

| VSBU_PIN_ABS                | Max voltage on SBU1 and SBU2 pins                                                  | _                   | ı   | 24                      | V    |                                                                                                        |

| VGPIO_OVT_ABS               | OVT pins (16, 17) voltage                                                          | -0.5                | ı   | 6                       |      | _                                                                                                      |

| T <sub>A</sub>              | Internal system ambient temperature                                                | -40                 | _   | 55                      | °C   | Ambient temp inside system enclosure                                                                   |

| T <sub>J</sub>              | Junction temperature                                                               | -40                 | -   | 125                     |      | -                                                                                                      |

#### Notes

<sup>4.</sup> Usage above the absolute maximum conditions listed in Table 5 may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods of time may affect device reliability. The maximum storage temperature is 150 °C in compliance with JEDEC Standard JESD22-A103, High Temperature Storage Life. When used below absolute maximum conditions but above normal operating conditions, the device may not operate to specification.

<sup>5.</sup> In a system, if the negative spike exceeds the minimum voltage specified here, it is recommended to add Schottky diode to clamp the negative spike.

## **Device-Level Specifications**

All specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  55 °C and T<sub>J</sub>  $\leq$  125 °C, except where noted. Specifications are valid for 3.0 V to 5.5 V except where noted.

DC Specifications

**Table 6. DC Specifications (Operating Conditions)**

| Spec ID        | Parameter                   | Description                                                                       | Min                        | Тур               | Max              | Unit | Details/Conditions                                                                                                                                                                                                                                                                                 |  |

|----------------|-----------------------------|-----------------------------------------------------------------------------------|----------------------------|-------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SID.PWR#23     | V <sub>SYS_UFP</sub>        | VSYS valid range                                                                  | 2.75                       | _                 | 5.5              |      | UFP applications                                                                                                                                                                                                                                                                                   |  |

| SID.PWR#23_A   | V <sub>SYS_UFP_DRP</sub>    | -                                                                                 | 3                          | _                 | 5.5              |      | DFP/DRP applications                                                                                                                                                                                                                                                                               |  |

| SID.PWR#22     | VBUS_C                      | VBUS_C Port 0/1 valid range                                                       | 4                          | _                 | 21.5             |      | _                                                                                                                                                                                                                                                                                                  |  |

| SID.PWR#22A    | VBUS_MAX                    | Max VBUS_C_P0/1 voltage relative to VSS                                           | ı                          | _                 | 24               | V    | <ul> <li>-40 °C to +55 °C T<sub>A</sub>, Absolute</li> <li>Maximum</li> <li>A far-end short through cable resulting in a maximum of 30V allowed with the following conditions:</li> <li>a. Max pulse-width of 2 at 27V</li> <li>b. No more than 1000 times during the entire life-cycle</li> </ul> |  |

| SID.PWR#24     | VBUS_P                      | VBUS_P Port 0/1 valid range                                                       | 4.9                        | _                 | 5.5              |      | This is not a power pin.                                                                                                                                                                                                                                                                           |  |

| SID.PWR#1      | $V_{\mathrm{DDD}}$          | Regulated output voltage when V <sub>SYS</sub> powered                            | V <sub>SYS</sub> -<br>0.05 | -                 | V <sub>SYS</sub> |      | –40 °C ≤ T <sub>A</sub> ≤ +55 °C                                                                                                                                                                                                                                                                   |  |

| SID.PWR#1_A    | $V_{DDD}$                   | Regulated output voltage when V <sub>BUS</sub> powered                            | 3                          | -                 | 3.65             |      | -40 °C ≤ T <sub>A</sub> ≤ +55 °C                                                                                                                                                                                                                                                                   |  |

| SID.PWR#26     | V <sub>5V</sub>             | _                                                                                 | 4.85                       | _                 | 5.5              |      | _                                                                                                                                                                                                                                                                                                  |  |

| SID.PWR#13     | $V_{DDIO}$                  | Supply voltage for I/O                                                            | $V_{DDD}$                  | _                 | $V_{DDD}$        |      | $-40 \text{ °C} \le T_A \le +55 \text{ °C}, \text{ All V}_{DDD}$                                                                                                                                                                                                                                   |  |

| SID.PWR#24     | V <sub>CCD</sub>            | Regulated output voltage (for Core Logic)                                         | ı                          | 1.8               | -                |      | _                                                                                                                                                                                                                                                                                                  |  |

| SID.PWR#15     | C <sub>EFC</sub>            | Regulator bypass capacitor for V <sub>CCD</sub>                                   | ı                          | 100               | ı                | nF   | X5R ceramic                                                                                                                                                                                                                                                                                        |  |

| SID.PWR#16     | C <sub>EXC</sub>            | Power Supply decoupling capacitor for V <sub>DDD</sub>                            | ı                          | 1                 | -                | μF   | AJN Ceramic                                                                                                                                                                                                                                                                                        |  |

| Active Mode, V | <sub>SYS</sub> = 2.75 V to  | 5.5 V. Typical values measur                                                      | ed at V <sub>S</sub>       | <sub>YS</sub> = 3 | .3 V             |      |                                                                                                                                                                                                                                                                                                    |  |

| SID.PWR#4      | I <sub>DD12</sub>           | Supply current                                                                    | -                          | 10                | -                | mA   | T <sub>A</sub> = 25 °C, CC I/O IN Transmit or<br>Receive, no I/O sourcing current,<br>CPU at 24 MHz, PD port active                                                                                                                                                                                |  |

| Deep Sleep Mod | de, V <sub>SYS</sub> = 2.75 | V to 3.6 V                                                                        |                            |                   |                  |      |                                                                                                                                                                                                                                                                                                    |  |

| SID34          | I <sub>DD29</sub>           | V <sub>SYS</sub> = 2.75 to 3.6 V, I <sup>2</sup> C, wakeup and WDT on.            | ı                          | 150               | -                | μA   | V <sub>SYS</sub> = 3.3 V, T <sub>A</sub> = 25 °C                                                                                                                                                                                                                                                   |  |

| SID_DS1        | I <sub>DD_DS1</sub>         | V <sub>SYS</sub> = 3.3 V, CC wakeup on,<br>Type-C not connected.                  | _                          | 200               | -                | μА   | Power source = $V_{SYS}$ , Type-C not attached, CC enabled for wakeup, $R_P$ and $R_D$ connected at 70-ms intervals by CPU. $R_D$ connection should be enabled by both PD ports.                                                                                                                   |  |

| SID_DS3        | I <sub>DD_DS2</sub>         | V <sub>SYS</sub> = 3.3 V, CC wakeup on,<br>DP/DM, SBU ON with<br>NGDO/CSA/UVOV On | -                          | 500               | -                |      | One Port attached, Chip in Deep-sleep                                                                                                                                                                                                                                                              |  |

| XRES Current   |                             |                                                                                   |                            |                   |                  |      |                                                                                                                                                                                                                                                                                                    |  |

| SID307         | I <sub>DD_XR</sub>          | Supply current while XRES asserted                                                | _                          | 130               | _                | μA   | Power Source = V <sub>SYS</sub> = 3.3 V,<br>Type-C Not Attached, T <sub>A</sub> = 25 °C                                                                                                                                                                                                            |  |

CPU

Table 7. CPU Specifications (Guaranteed by Characterization)

| Spec ID    | Parameter              | Description                                               | Min | Тур | Max | Unit | Details/Conditions                                    |

|------------|------------------------|-----------------------------------------------------------|-----|-----|-----|------|-------------------------------------------------------|

| SID.CLK#4  | F <sub>CPU</sub>       | CPU input frequency                                       | _   | _   | 48  | MHz  | –40 °C ≤T <sub>A</sub> ≤ +55 °C, All V <sub>DDD</sub> |

| SID.PWR#21 | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep mode                               | _   | 35  | _   | ш    |                                                       |

| SYS.XRES#5 | T <sub>XRES</sub>      | External reset pulse width                                | 5   | _   | _   |      | Guaranteed by                                         |

| SYS.FES#1  | T_PWR_RDY              | Power-up to "Ready to accept I <sup>2</sup> C/CC command" | _   | 5   | 25  | ms   | characterization                                      |

**GPIO**

Table 8. GPIO DC Specifications

| Spec ID     | Parameter                  | Description                                        | Min                         | Тур | Max                        | Unit | Details/Conditions                                                                                      |

|-------------|----------------------------|----------------------------------------------------|-----------------------------|-----|----------------------------|------|---------------------------------------------------------------------------------------------------------|

| SID.GIO#37  | V <sub>IH_CMOS</sub>       | Input voltage HIGH threshold                       | 0.7 ×<br>V <sub>DDIO</sub>  | _   | _                          |      | CMOS input                                                                                              |

| SID.GIO#38  | V <sub>IL_CMOS</sub>       | Input voltage LOW threshold                        | ı                           | _   | 0.3 ×<br>V <sub>DDIO</sub> |      | CiviOS iriput                                                                                           |

| SID.GIO#39  | V <sub>IH_VDDIO2.7</sub> - | LVTTL input, V <sub>DDIO</sub> < 2.7 V             | 0.7 ×<br>V <sub>DDIO</sub>  | -   | _                          |      | _                                                                                                       |

| SID.GIO#40  | V <sub>IL_VDDIO2.7</sub> - | LVTTL input, V <sub>DDIO</sub> < 2.7 V             | ı                           | ı   | 0.3 ×<br>V <sub>DDIO</sub> | V    | _                                                                                                       |

| SID.GIO#41  | V <sub>IH_VDDIO2.7+</sub>  | LVTTL input, $V_{DDIO} \ge 2.7 \text{ V}$          | 2.0                         | _   | _                          |      | _                                                                                                       |

| SID.GIO#42  | V <sub>IL_VDDIO2.7+</sub>  | LVTTL input, $V_{DDIO} \ge 2.7 \text{ V}$          | _                           | _   | 0.8                        |      | _                                                                                                       |

| SID.GIO#33  | V <sub>OH_3V</sub>         | Output voltage HIGH level                          | V <sub>DDIO</sub> – 0.6     | -   | -                          |      | I <sub>OH</sub> = –4 mA at 3-V V <sub>DDIO</sub>                                                        |